## Generation of Accurate On-Chip Transconductances Using a Monolithic CMOS PLL With Hybrid Analog and Digital Control

. . .

by

## **Angus McLaren**

A Thesis submitted in conformity with the requirements for the degree of Master of Applied Science Department of Electrical and Computer Engineering University of Toronto

© Copyright Angus McLaren, 2000

#### National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Otlaws ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérence

Our lie Notre rélérance

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-50388-7

# Canadä

## Generation of Accurate On-Chip Transconductances Using a Monolithic CMOS PLL With Hybrid Analog and Digital Control

Abstract

Angus McLaren Department of Electrical and Computer Engineering University of Toronto Degree of Master of Applied Science, 2000

## Abstract

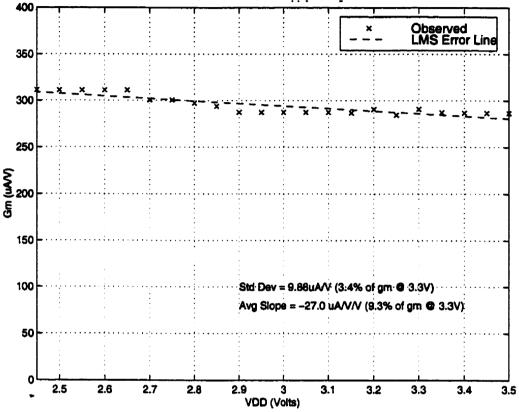

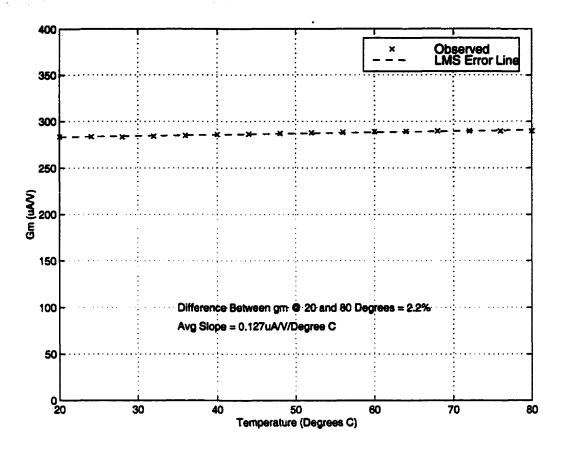

A method for generating accurately-known on-chip transistor transconductances over process, power-supply, and temperature variations is presented. The technique uses an adjustable constant- $g_m$  bias circuit, which is tuned with a fully-integrated CMOS PLL locked to an external frequency reference normally present to produce a system clock. The PLL uses a charge-pump structure with three control-loops (two digital and one analog) having overlapping ranges with hysteresis to minimize tuning glitches in steady-state. The PLL has a lock-range of 135 MHz to 300 MHz, and displays an RMS jitter of 15.6 ps. The transconductances generated from the circuit display a 2.2% variation for a 60°C change in temperature, and a 1.3% variation for a 10% variation in power-supply voltage. The design has been fabricated in a 0.35  $\mu$ m CMOS process, using an active area of 1200 x 1200  $\mu$ m<sup>2</sup>, and drawing 5.8 mA from a 3.3 V supply.

## **Acknowledgments**

I would like to thank my supervisor, Ken Martin, whose ideas this work was based on. I am deeply indebted to him for the opportunities he gave me, and the invaluable knowledge he has passed on to me.

Thanks to the EA104 posse for providing a lively (sometimes exceedingly) work environment, indispensable technical and emotional support, and, of course, friendship. Afshin, Amir, Anas, Anthony, Augustine, Bahram, Cameron, Dave, Dickson (all versions), Fabio the Incredible, James, John, Kamran, Professor Phang, Mark (both Irish and not), Raj, Saman, Sebastian, Shahriar, Steve, Takis, Vasilis: may all your DRC's run clean!

I am very grateful to NSERC and the University of Toronto for their financial support, and to Micronet for their fabrication services. Thanks also to Professor Salama for allowing me access to his test equipment.

Thanks also to Professor Salama for giving me permission to use his test equipment, and Jaro Pristupa for maintaining the CAD tools, as well as tracking down test equipment for me.

I would also like to express my gratitude to my father, who has kept up interest in my work over the past two years, despite its lying a great distance outside his field of expertise.

Finally, and most importantly, I would like to thank my fiance Maia, without whose support and understanding I could not have completed this work.

<u>\_</u>+

ę

# Table of Contents

| 1. Introduction                                                    | 1    |

|--------------------------------------------------------------------|------|

| 1.1 Generation of Accurate Transistor Transconductance             | 1    |

| 1.1.1 Motivation and Design Implications                           |      |

| 1.1.2 Constant-Transconductance Bias Circuit                       | -    |

| 1.1.3 Constant-g <sub>m</sub> Bias Circuit With PLL-Tuned Resistor |      |

|                                                                    | -    |

| 1.2 Intended Application: Wireless Data Communications Receiver    | _    |

| 1.3 Outline of Thesis                                              |      |

| 1.4 References                                                     | . 3  |

| 2. Phase-Locked Loops: A Background                                | б    |

| 2.1 Basic Loop Structure                                           | 6    |

| 2.1.1 Block Diagram                                                | -    |

| 2.1.2 Classes of PLL Systems                                       | _    |

| 2.1.3 Linearized Small-Signal Model                                | _    |

| 2.1.4 Lock Metrics                                                 |      |

| 2.1.4.1 Lock-in Range                                              |      |

| 2.1.4.2 Hold Range                                                 |      |

| 2.1.4.3 Pull-in Range                                              |      |

| 2.1.4.4 Pull-out Range                                             |      |

| 2.2 Block Realizations                                             |      |

| 2.2.1 Phase-Frequency Detector With Charge-Pump                    | . 12 |

| 2.2.1.1 Phase-Frequency Detector                                   |      |

| 2.2.1.2 Charge Pump for PFD                                        |      |

| 2.2.2 Loop Filter                                                  |      |

| 2.2.3 Voltage-Controlled Oscillator                                |      |

| 2.2.3.1 LC Oscillators                                             |      |

| 2.2.3.2 RC Multivibrators                                          |      |

| 2.2.3.3 Ring Oscillators                                           |      |

| 2.2.4 Frequency Dividers                                           |      |

| 2.2.5 Loop Equations for Charge-Pump PLL With Lead-Lag Loop Filter |      |

| 2.3 Design Issues                                                  |      |

| 2.3.1 Loop Bandwidth                                               |      |

| 2.3.2 Quality Factor and Natural Frequency                         |      |

| 2.3.3 PFD                                                          |      |

| 2.3.3.1 Lock Behaviour                                             |      |

| 2.3.3.2 Logic Family                                               |      |

| 2.3.4 Charge-Pump                                                  |      |

| 2.3.4.1 Up/Down Symettry                                           |      |

| 2.3.4.2 Variation of Up/Down Currents                              |      |

| 2.3.5 VCO                                                          |      |

| 2.3.5.1 Jitter                                                     |      |

| 2.3.5.2 Frequency-Control Voltage Characteristic                   | . 24 |

| Tal | ble | of Contents |  |

|-----|-----|-------------|--|

~ ...

| 2.3.6 Integration of Loop Filter                      | 24  |

|-------------------------------------------------------|-----|

| 2.3.7 Loop Gain                                       | 24  |

| 2.4 References                                        | 29  |

|                                                       |     |

| 3. Block-Level Modeling and Design                    | 31  |

| 3.1 PLL Simulation Problems                           | 31  |

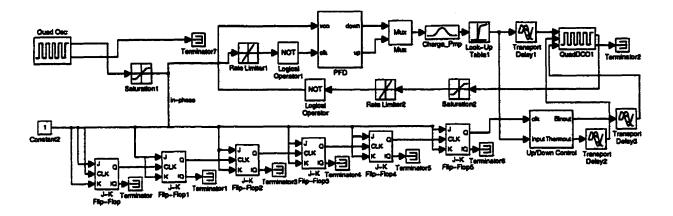

| 3.2 System Block-Level Description                    | 32  |

| 3.2.1 System Description                              | 32  |

| 3.2.2 System Advantages                               | 34  |

| 3.3 Blocks                                            | 34  |

| 3.3.1 VCO                                             | 35  |

| 3.3.2 Phase Detector                                  | 36  |

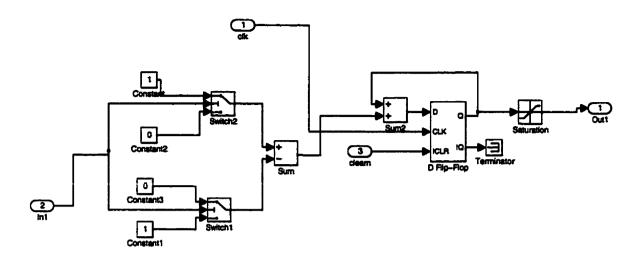

| 3.3.3 Up/Down Control                                 | 43  |

| 3.4 SIMULINK Model                                    | 45  |

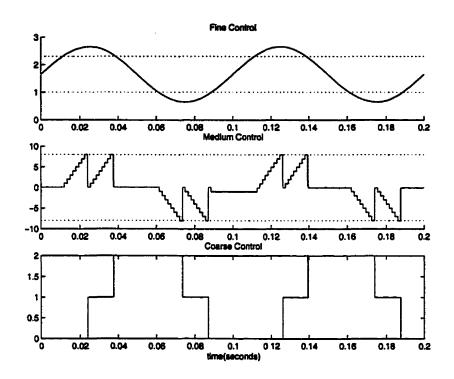

| 3.5 SIMULINK Simulation Results                       | 46  |

|                                                       | 46  |

| 3.5.1 System With No Delay                            | 50  |

| 3.5.2 System With Delay                               | 52  |

| 3.6 References                                        | 54  |

|                                                       | E A |

| 4. Circuit Design                                     | 54  |

| 4.1 Overall System                                    | 54  |

| 4.2 Adjustable Constant-Transconductance Bias Circuit | 55  |

| 4.2.1 Bias Circuit Without Variable Resistor          | 56  |

| 4.2.2 Voltage-Controlled Resistor                     | 61  |

| 4.3 Transconductance-Controlled Oscillator            | 64  |

| 4.3.1 Oscillator Design                               | 64  |

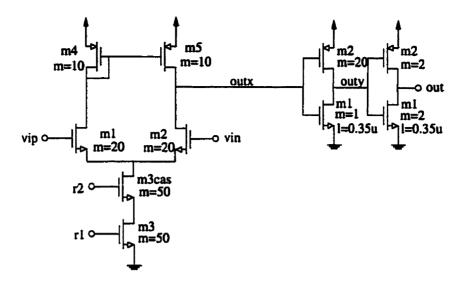

| 4.3.2 Oscillator Buffer Design                        | 69  |

| 4.4 Phase-Frequency Detector                          | 70  |

| 4.5 Charge-Pump                                       | 76  |

| 4.5.1 Charge-Pump Design                              | 76  |

| 4.5.2 Loop-Filter Design and Self-Biasing             | 80  |

| 4.6 Comparators                                       | 82  |

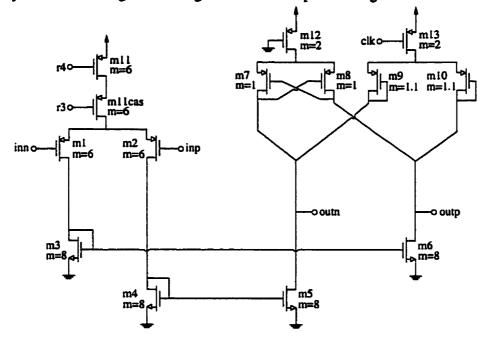

| 4.6.1 Comparator 1 Design                             | 83  |

| 4.6.2 Comparator 2 Design                             | 85  |

| 4.7 Up/Down Control Logic                             | 87  |

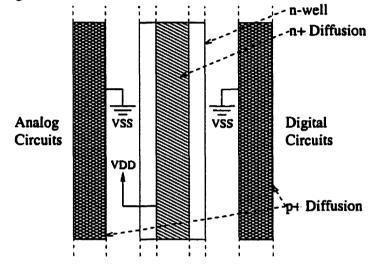

| 4.8 Layout Considerations                             | 88  |

| 4.9 References                                        | 91  |

|                                                       |     |

| 5 Measurements for Enbricated VCO and DIT             | 93  |

| 5. Measurements for Fabricated VCO and PLL            |     |

| 5.1 VCO                                               | 93  |

| 5.1.1 Test Setup                                      | 95  |

| 5.1.2 Results                                         | 96  |

| 5.2 Entire PLL                                        | 101 |

| 5.2.1 Test Setup                                      | 105 |

|                                                       |     |

٦.

| 5.2.2 Results                                                                                            |            |

|----------------------------------------------------------------------------------------------------------|------------|

| 6. Conclusions<br>6.1 Discussion<br>6.2 Suggestions for Future Work<br>6.3 References                    | 122<br>123 |

| Appendix A: VHDL Code for Up/Down Logic<br>Appendix B: Derivation of Delay Through Differential Inverter |            |

# List of Tables

## **Chapter 2: Phase-Locked Loops: A Background**

| Table 2.1: State Assignment for PFD                     | 13 |

|---------------------------------------------------------|----|

| Table 2.2: Formulae for PFD and Passive Lead-Lag Filter | 19 |

| Table 2.3: Parameter Values Used for Root Locus Plot    | 24 |

|                                                         |    |

## **Chapter 4: Circuit Design for Hybrid Analog/Digital PLL**

| Table 4.1: Opamp Characteristics        | 58 |

|-----------------------------------------|----|

| Table 4.2: Characteristics of Bias Loop | 60 |

## **Chapter 5: Measurements for Fabricated VCO and PLL**

| Table 5.1: Summar | y of PLL and Bias S | ystem Performance | 120 |

|-------------------|---------------------|-------------------|-----|

|-------------------|---------------------|-------------------|-----|

# List of Figures

## **Chapter 1: Introduction**

| Figure 1.1: Simplified Schematic of Constant-Transconductance Bias Circuit | 2 |

|----------------------------------------------------------------------------|---|

| Figure 1.2: Schematic for Proposed System                                  | 3 |

| Figure 1.3: Simplified Schematic for PLL                                   | 4 |

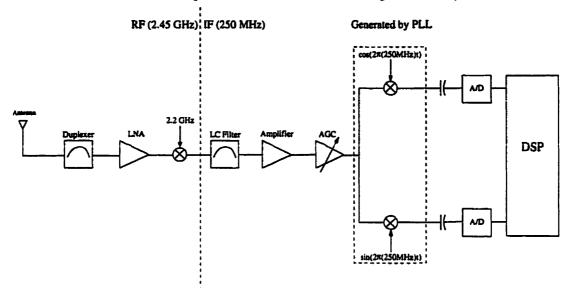

| Figure 1.4: System Schematic for Low-Cost Wireless Receiver                | 5 |

## **Chapter 2: Phase-Locked Loops: A Background**

| Figure 2.1: Block Diagram for General PLL                                                | 7  |

|------------------------------------------------------------------------------------------|----|

| Figure 2.2: Simplified Charge-Pump Circuit                                               | 8  |

| Figure 2.3: Block Diagram for Linearized PLL                                             | 9  |

| Figure 2.4: Schematic for PFD                                                            | 12 |

| Figure 2.5: Signal-Flow Graph for PFD                                                    | 13 |

| Figure 2.6: PFD Characteristic: a) Ideal(Upper) b) Non-Zero Delay in Logic (Lower)       | 14 |

| Figure 2.7: Lead-Lag Loop Filter                                                         | 15 |

| Figure 2.8: Schematic for Lead-Lag Loop Filter for Charge-Pump PLL (Two Realizations)    | 15 |

| Figure 2.9: Schematic for Current-Starved Delay Element                                  | 17 |

| Figure 2.10: Circuit Schematic for Differential Inverter                                 | 18 |

| Figure 2.11: Root Locus Plot for Third-Order System                                      | 25 |

| Figure 2.12: Behaviour of Root Loci for Varying Values of C <sub>1</sub> /C <sub>2</sub> | 26 |

| Figure 2.13: Step Response for PLL.                                                      | 27 |

| Figure 2.14: Step Response of PLL at Input to VCO                                        | 27 |

| Figure 2.15: Pole-Zero Plot for Filter 1                                                 | 28 |

| Figure 2.16: Bode Plot for PLL With Filter 1                                             | 28 |

| Figure 2.17: Bode Plot of PLL at Input to VCO                                            | 29 |

|                                                                                          |    |

## Chapter 3: System-Level Design for Hybrid Analog/Digital PLL

| Figure 3.1: Simplified Schematic of System                                   | 32 |

|------------------------------------------------------------------------------|----|

| Figure 3.2: Frequency Plan for VCO                                           | 36 |

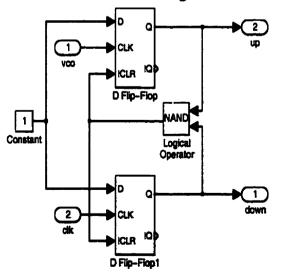

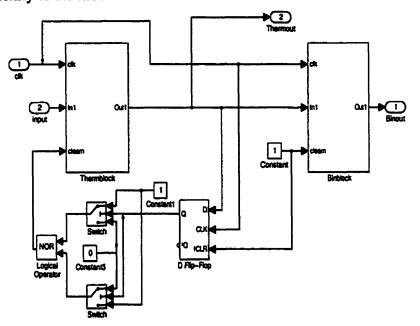

| Figure 3.3: SIMULINK Schematic for PFD                                       | 36 |

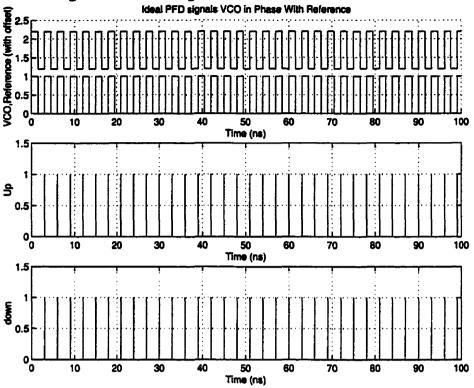

| Figure 3.4: Ideal PFD Signals for VCO in Phase With Reference Signal         | 37 |

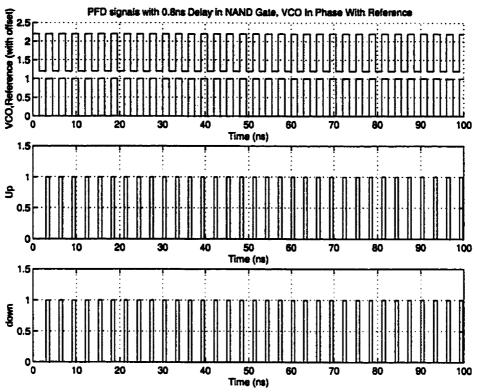

| Figure 3.5: PFD Signals with Delay in NAND Gate, VCO In Phase With Reference | 38 |

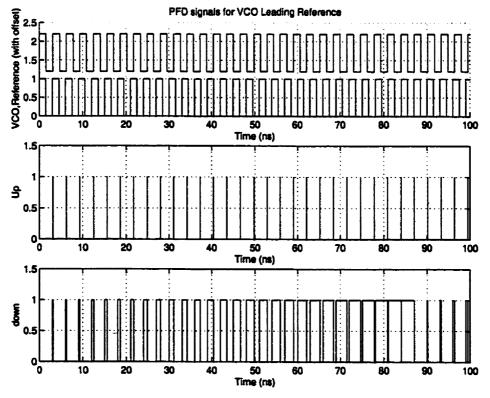

| Figure 3.6: Ideal Response of PFD for $f_{VCO} > f_{Ref}$                    | 38 |

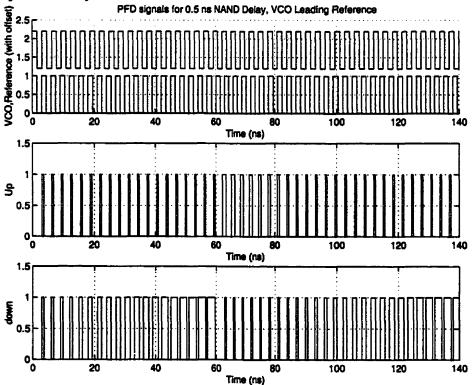

| Figure 3.7: PFD Signals with 0.5 ns NAND Delay, $f_{VCO} > f_{Ref}$          | 39 |

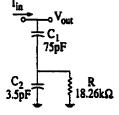

| Figure 3.8: Loop Filter Used for SIMULINK Simulations                        | 40 |

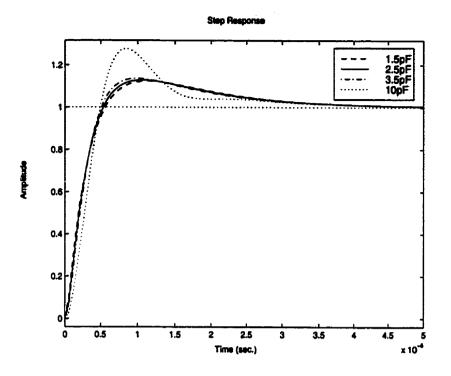

| Figure 3.9: Step Responses for Various Values of C <sub>2</sub>              | 42 |

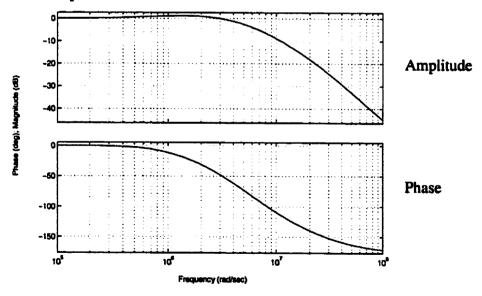

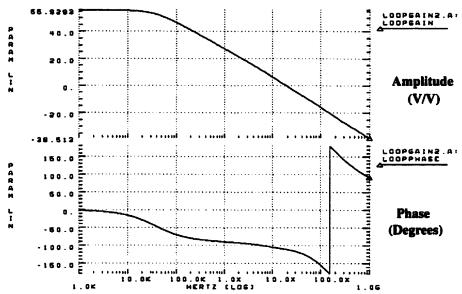

| Figure 3.10: Bode Plots for PLL System Design                                | 42 |

| List   | of | Fier | ine | ė. |

|--------|----|------|-----|----|

| STATE: | ~  | ~    |     |    |

- -2-----

| Figure 3.11: Block Diagram of Up/Down Control Block                                | 43 |

|------------------------------------------------------------------------------------|----|

| Figure 3.12: Block Diagram of Thermblock (Same as Binblock)                        | 44 |

| Figure 3.13: Signals for Up/Down Control Block                                     | 45 |

| Figure 3.14: Complete SIMULINK System                                              | 46 |

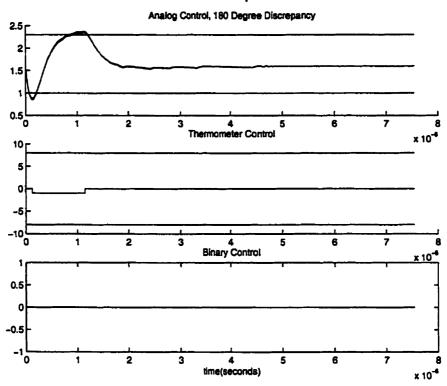

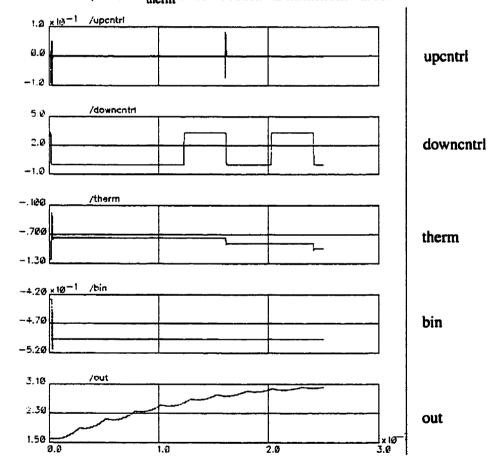

| Figure 3.15: System Response to 180 Degree Phase Error                             | 47 |

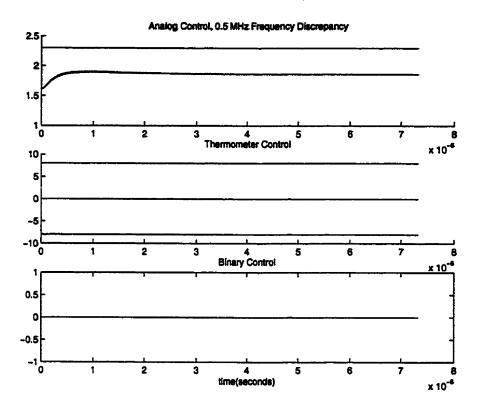

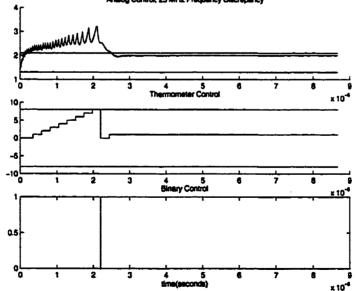

| Figure 3.16: System Response for 0.5 MHz Frequency Discrepancy                     | 48 |

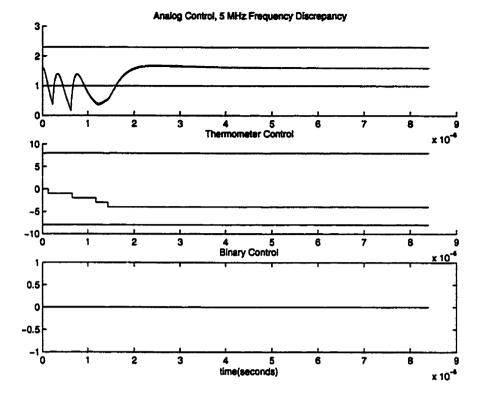

| Figure 3.17: System Response for Frequency Discrepancy of 5 MHz                    | 49 |

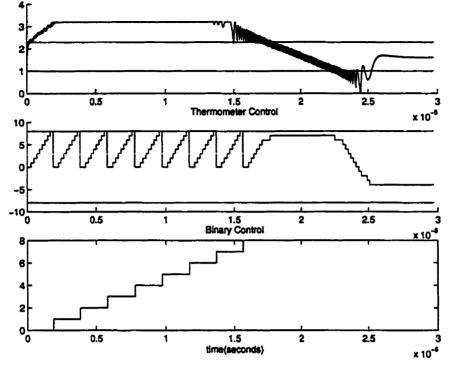

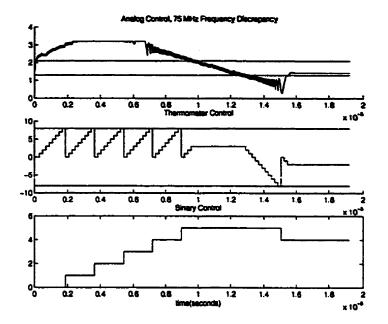

| Figure 3.18: System Response for 75 MHz Frequency Discrepancy                      | 50 |

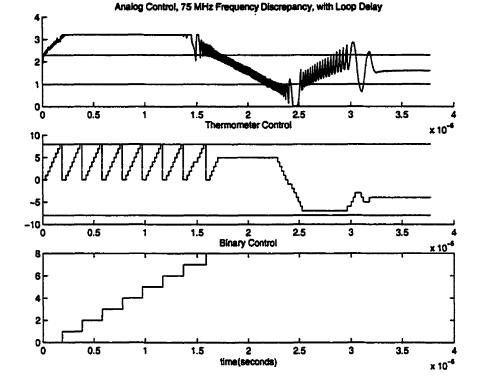

| Figure 3.19: System Response for 75 MHz Frequency Discrepancy and 75 ns Loop Delay | 51 |

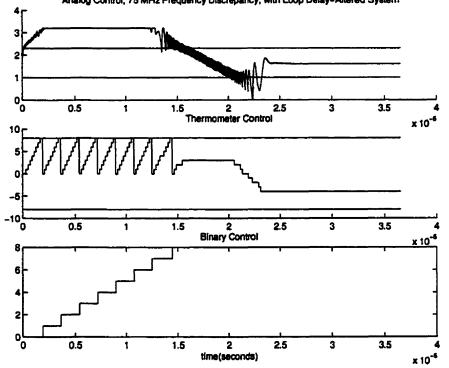

| Figure 3.20: Response of Altered System to 75 MHz                                  |    |

| Frequency Discrepancy and 75 ns Delay                                              | 52 |

|                                                                                    |    |

## Chapter 4: Circuit Design for Hybrid Analog/Digital PLL

| Figure 4.1: Simplified System Schematic                                             | 54 |

|-------------------------------------------------------------------------------------|----|

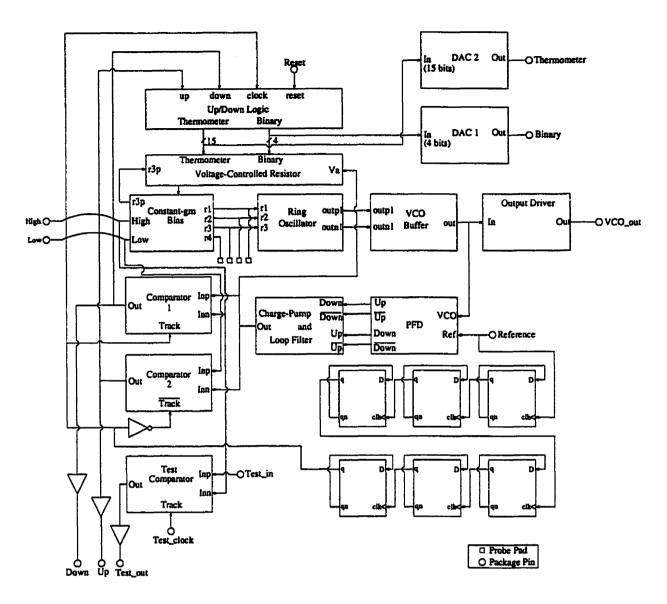

| Figure 4.2: Full System Block-Diagram                                               | 55 |

| Figure 4.3: Circuit Schematic for Adjustable Constant-Transconductance Bias Circuit | 57 |

| Figure 4.4: Measurement of Bias Circuit Loop Gain                                   | 59 |

| Figure 4.5: Frequency Response of Bias Loop                                         | 60 |

| Figure 4.6: Voltage-Controlled Resistor                                             | 61 |

| Figure 4.7: Response of Final System to 275 MHz Input                               | 62 |

| Figure 4.8: Response of Final System to 325 MHz Input                               | 63 |

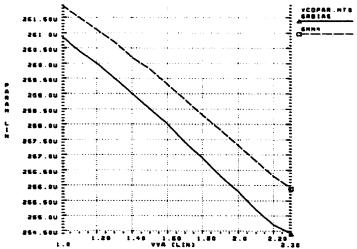

| Figure 4.9: Variable-Resistor Conductance and g <sub>m4</sub> Versus V <sub>a</sub> | 63 |

| Figure 4.10: G <sub>m</sub> CO Schematic                                            | 64 |

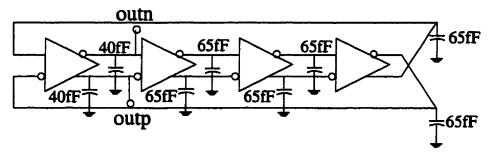

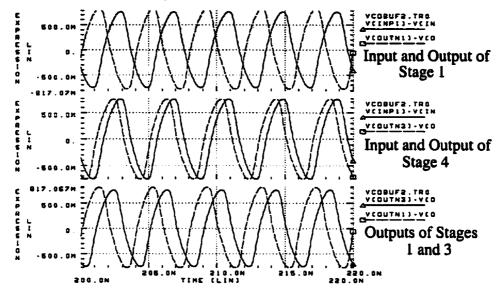

| Figure 4.11: Ring Oscillator Signals at Outputs of Various Stages                   | 65 |

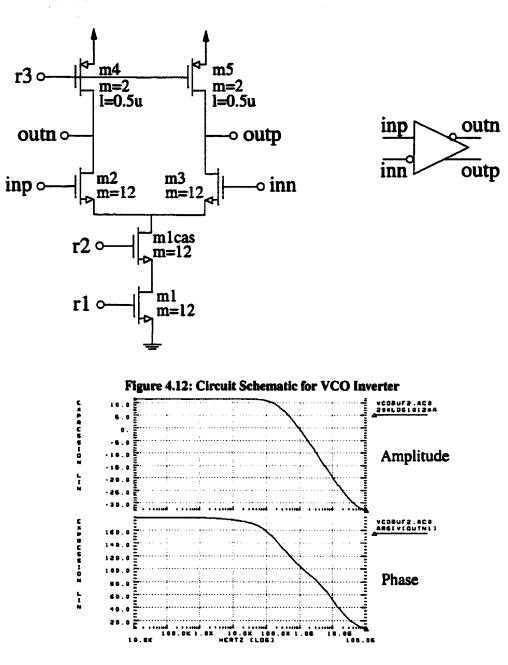

| Figure 4.12: Circuit Schematic for VCO Inverter                                     | 66 |

| Figure 4.13: Frequency Response of VCO Inverter                                     | 66 |

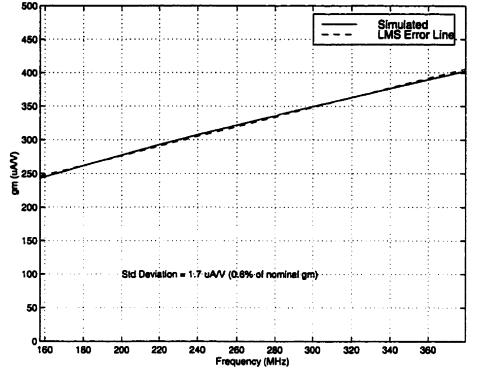

| Figure 4.14: Simulated Transconductance of mhigh Versus VCO Frequency               | 68 |

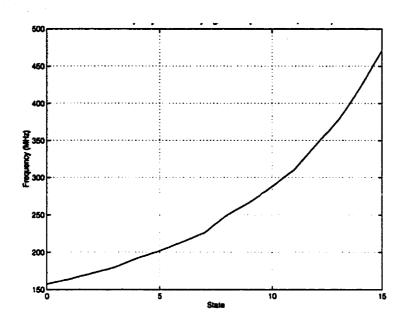

| Figure 4.15: VCO Frequency Versus Binary Control Signal (Analog and Thermometer     |    |

| Control Signals Fixed at Middle Values)                                             | 69 |

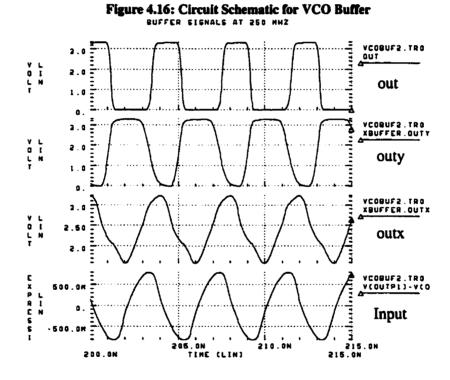

| Figure 4.16: Circuit Schematic for VCO Buffer                                       | 70 |

| Figure 4.17: VCO Buffer Signals                                                     | 70 |

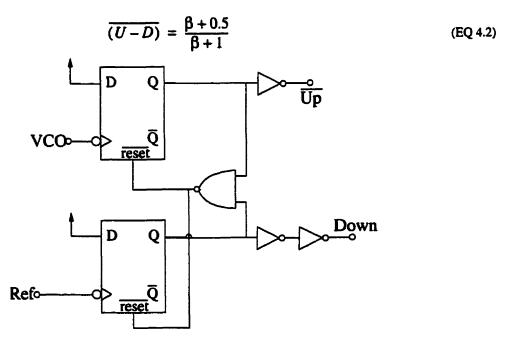

| Figure 4.18: Block Diagram for PFD                                                  | 71 |

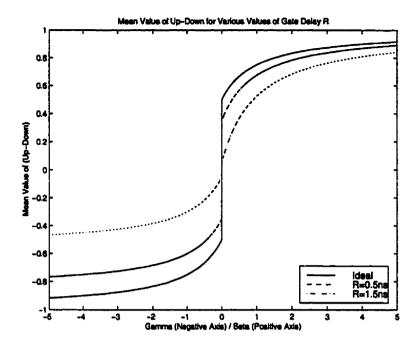

| Figure 4.19: Mean Value of (Up-Down) for Various Values of Gate Delay $\Delta R$    | 72 |

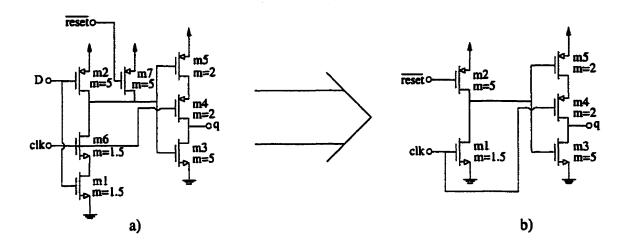

| Figure 4.20: Circuit Schematic for PFD Flip-Flop                                    | 74 |

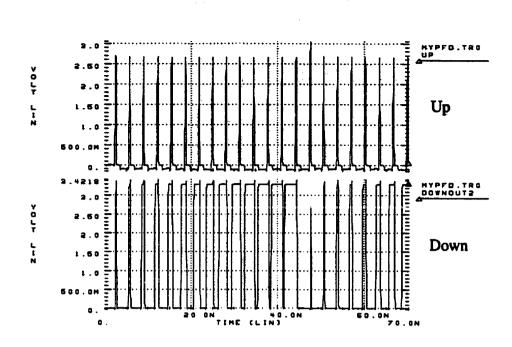

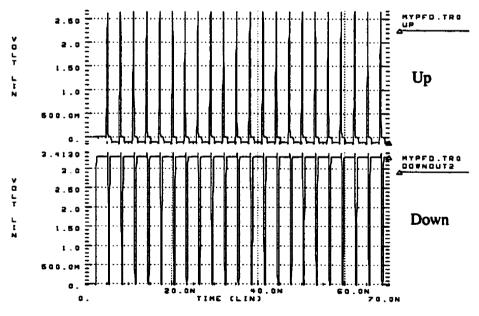

| Figure 4.21: PFD Response for $f_{VCO} > f_{Ref}$                                   | 75 |

| Figure 4.22: Response of PFD for Maximum Phase Error at 333.3 MHz                   | 75 |

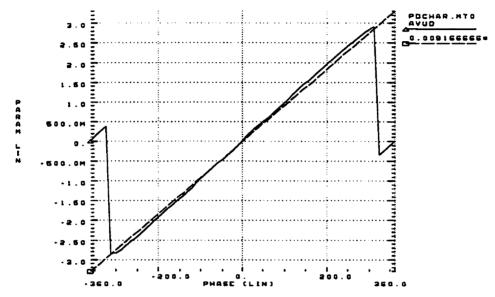

| Figure 4.23: Mean Value of Up-Down Versus Phase Error Between Inputs at 333 MHz     | 76 |

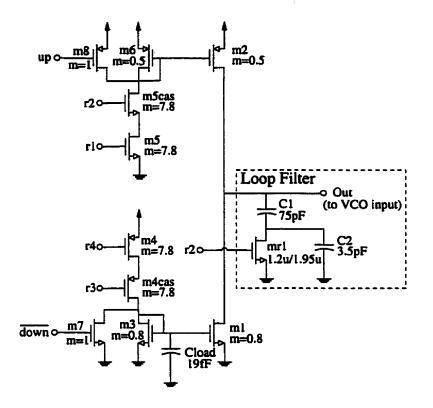

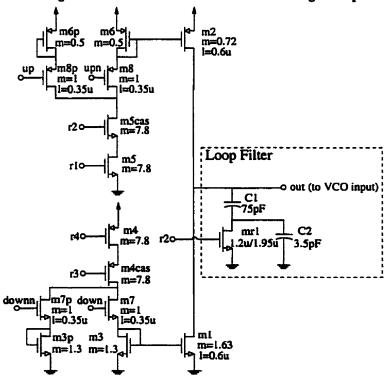

| Figure 4.24: Initial Circuit Schematic for Charge-Pump                              | 78 |

| Figure 4.25: Circuit Schematic for Revised Charge-Pump Design                       | 78 |

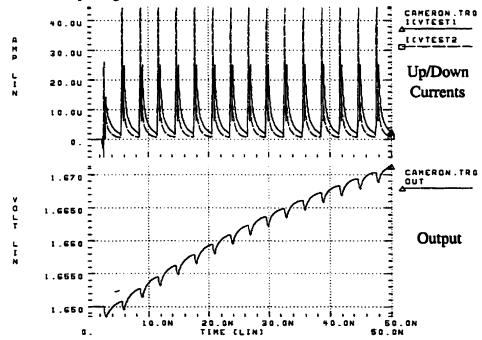

| Figure 4.26: Charge/Discharge Currents and Output Voltage of Charge-Pump            |    |

| List of Figures |   |    |    |   |   |      |

|-----------------|---|----|----|---|---|------|

|                 | ſ | İs | to | f | F | Ires |

| for Equal Input Frequencies                                                         | <b>79</b> |

|-------------------------------------------------------------------------------------|-----------|

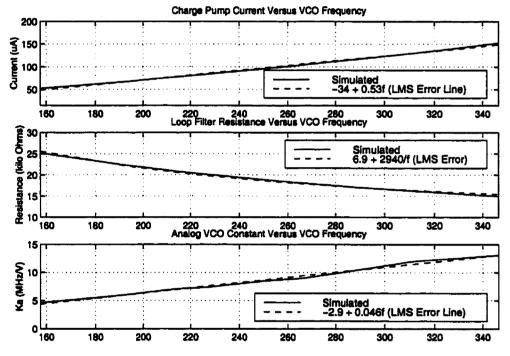

| Figure 4.27: Simulated I <sub>ch</sub> , R, and K <sub>a</sub> Versus VCO Frequency | 81        |

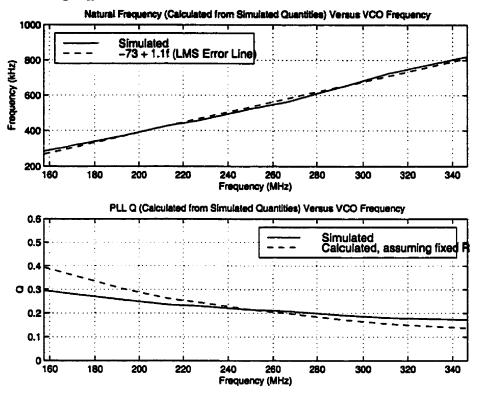

| Figure 4.28: Natural Frequency and Q Versus Frequency                               | 82        |

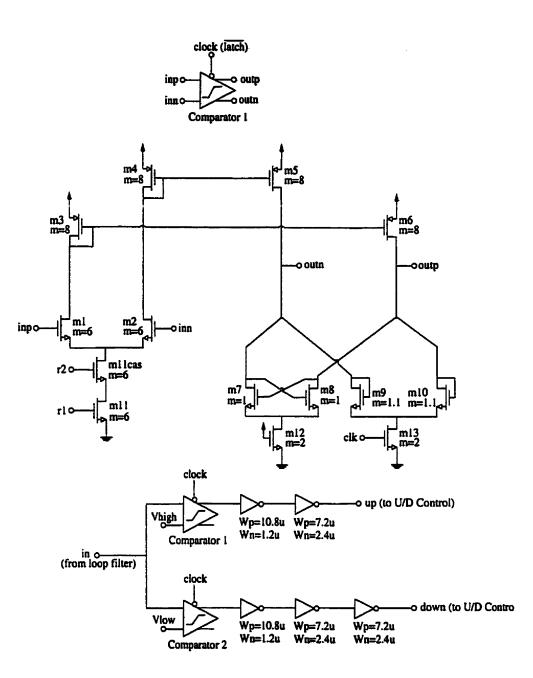

| Figure 4.29: Circuit Schematic for Comparator 1                                     | 84        |

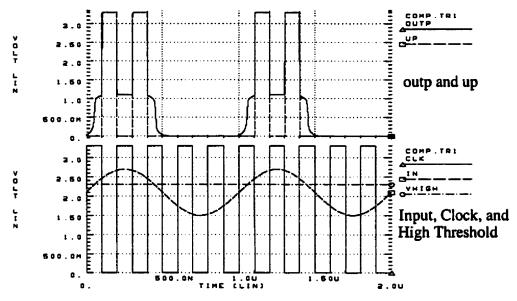

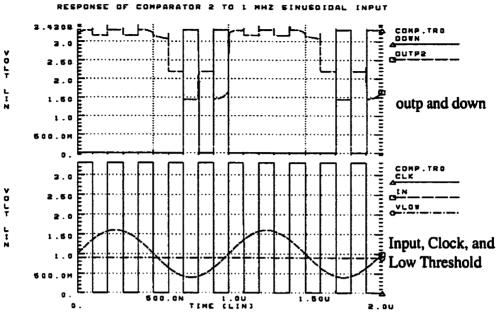

| Figure 4.30: Output of Comparator1 for 1 MHz Sinusoidal Input, 5 MHz Clock Rate     | 85        |

| Figure 4.31: Circuit Schematic for Comparator 2                                     | 86        |

| Figure 4.32: Output of Comparator 2 for 1 MHz Sinusoidal Input, 5 MHz Clock Rate    | 87        |

| Figure 4.33: Schematic for Guard Rings                                              | 88        |

| Figure 4.34: Open-Loop Response of PLL Without VCO                                  | 89        |

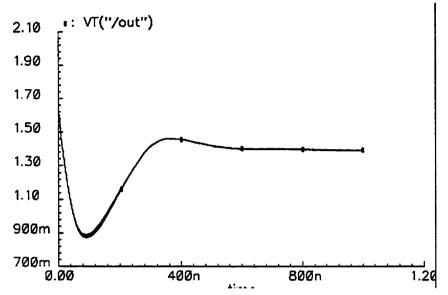

| Figure 4.35: Response of VCO Control Voltage in Analog PLL to 290.7 MHz Input       | 90        |

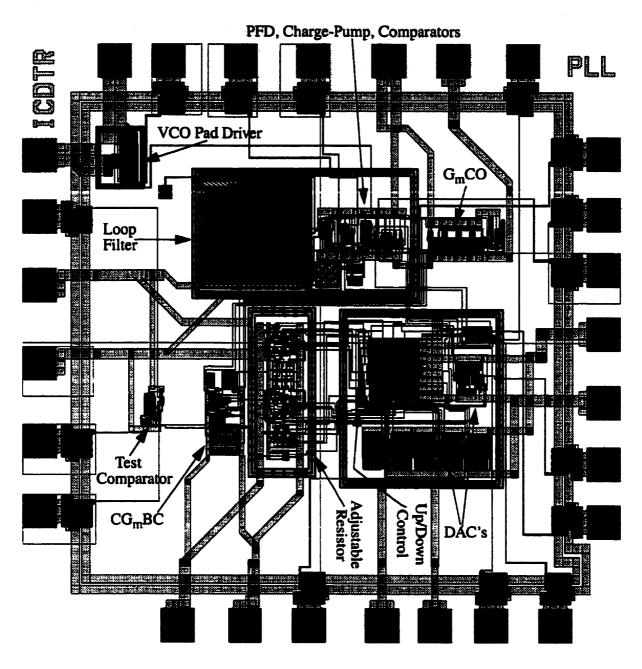

| Figure 4.36: Final Layout for PLL                                                   | 91        |

## **Chapter 5: Measurements for Fabricated VCO and PLL**

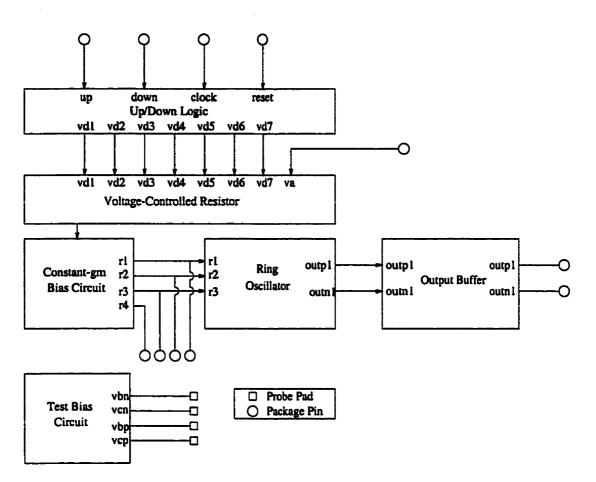

| Figure 5.1: Block Diagram of VCO Circuit                                           | 94         |

|------------------------------------------------------------------------------------|------------|

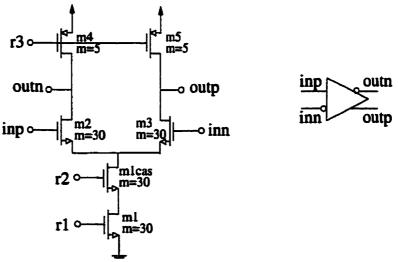

| Figure 5.2: Circuit Schematic for Ring Oscillator Inverter                         | 94         |

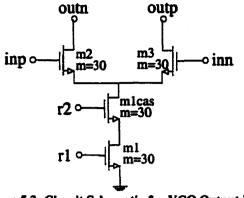

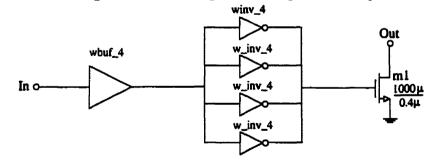

| Figure 5.3: Circuit Schematic for VCO Output Buffer                                | 95         |

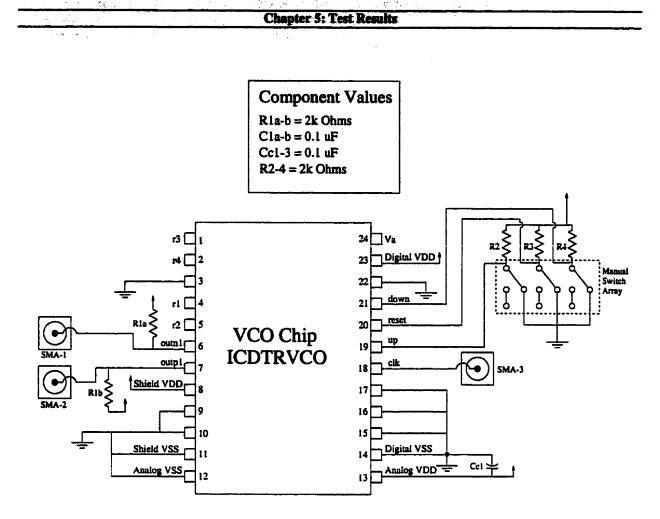

| Figure 5.4: PCB Layout for VCO Chip                                                | 96         |

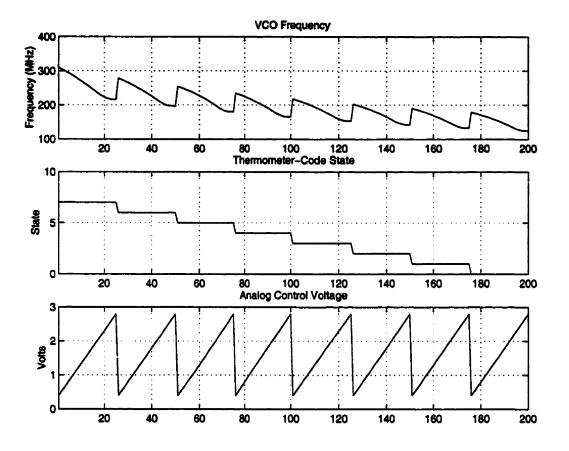

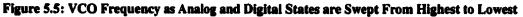

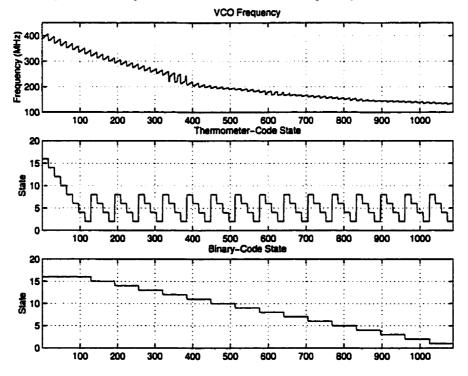

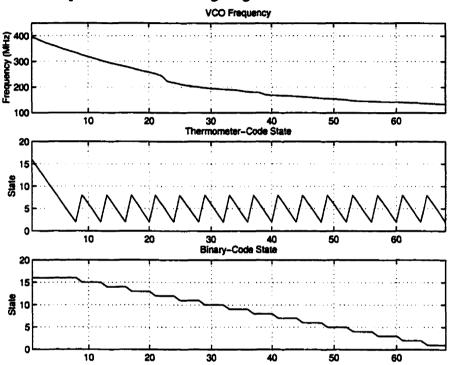

| Figure 5.5: VCO Frequency as Analog and Digital States are Swept Highest to Lowest | 97         |

| Figure 5.6: VCO Frequency Versus Digital State ( $V_a = 0.8 V$ )                   | <b>9</b> 8 |

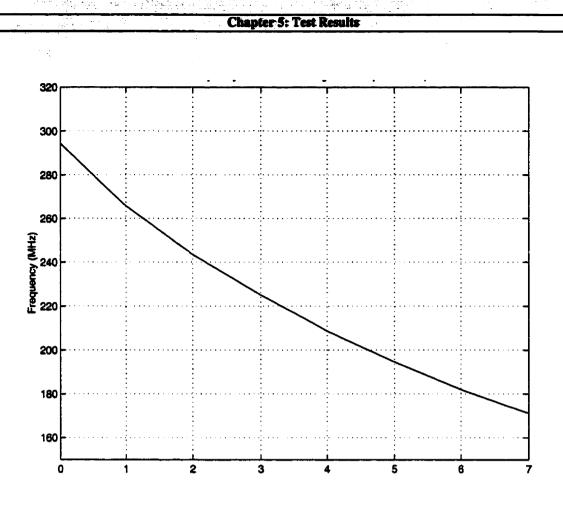

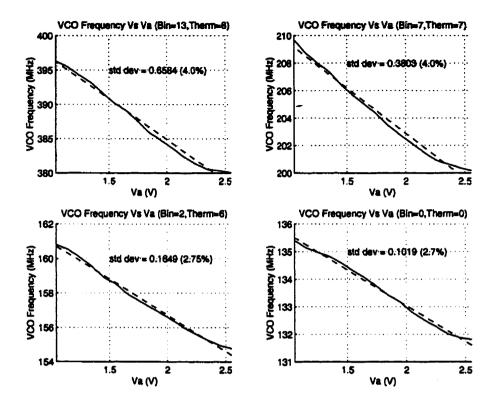

| Figure 5.7: VCO Frequency Versus Analog Control Voltage for Four Different         |            |

| Digital States                                                                     | <b>99</b>  |

| Figure 5.8: Analog VCO Constant Versus VCO Frequency                               | <b>99</b>  |

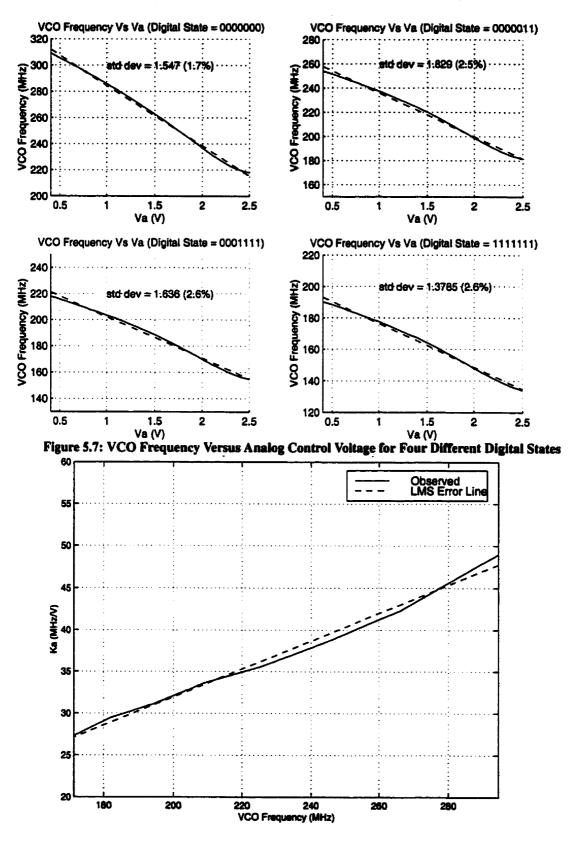

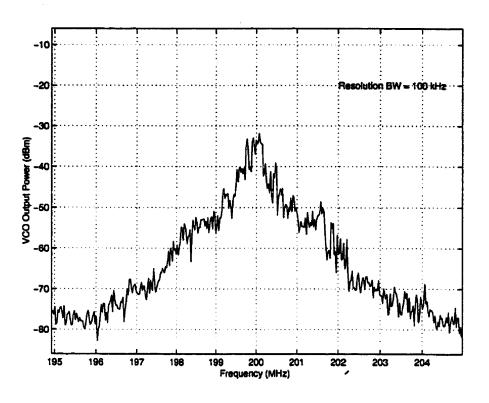

| Figure 5.9: Spectrum of VCO Output at 200 MHz                                      | 100        |

| Figure 5.10: Spectrum of VCO Output at 200 MHz (Zoomed In)                         | 101        |

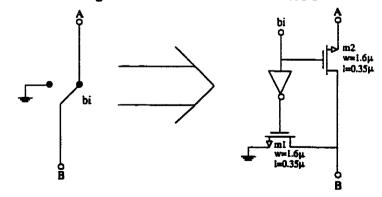

| Figure 5.11: Block Diagram for Complete PLL Chip                                   | 103        |

| Figure 5.12: Circuit Schematic for Output Driver                                   | 103        |

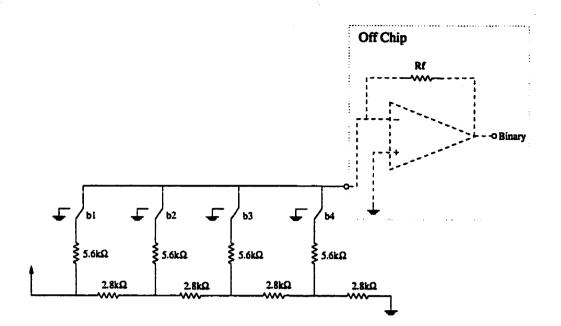

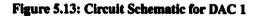

| Figure 5.13: Circuit Schematic for DAC 1                                           | 104        |

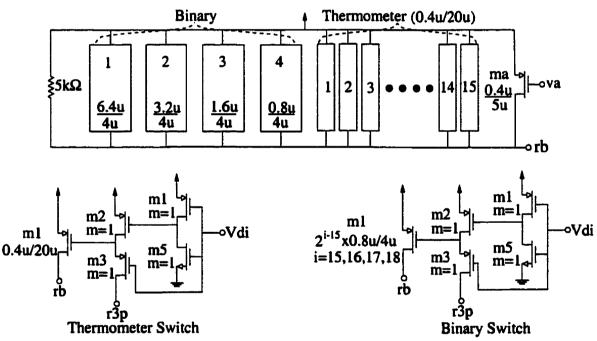

| Figure 5.14: Circuit Schematic for DAC 2                                           | 104        |

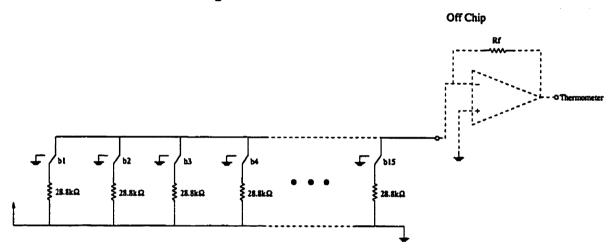

| Figure 5.15: Circuit Schematic for DAC Switches                                    | 104        |

| Figure 5.16: PCB Layout for PLL Chip                                               | 106        |

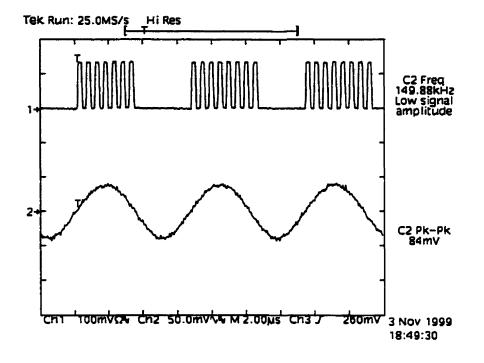

| Figure 5.17: Output of Test Comparator in Response to Sinusoidal Input             | 107        |

| Figure 5.18: Track Output for an Input Frequency of 650 MHz                        | 108        |

| Figure 5.19: Input (Upper Waveform) and Output (Lower Waveform)                    |            |

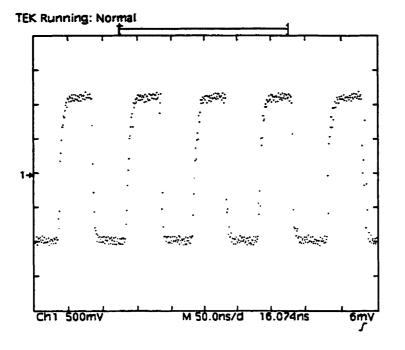

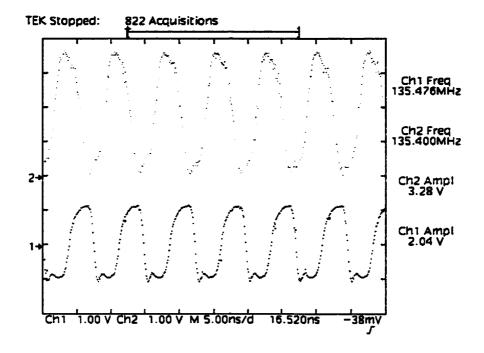

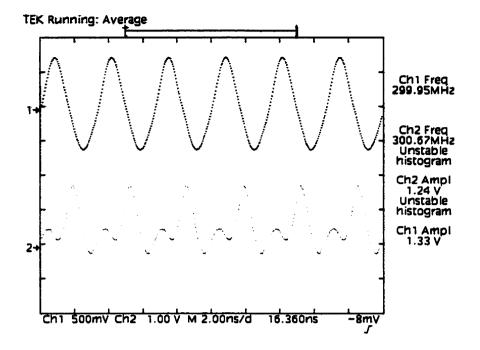

| for 135 MHz Input                                                                  | 109        |

| Figure 5.20: Input (Upper Waveform) and Output (Lower Waveform)                    |            |

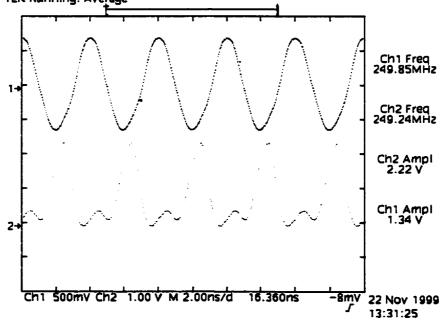

| for 250 MHz Input                                                                  | 109        |

| Figure 5.21: Input (Upper Waveform) and Output(Lower Waveform)                     |            |

| for 300 MHz Input                                                                  | 110        |

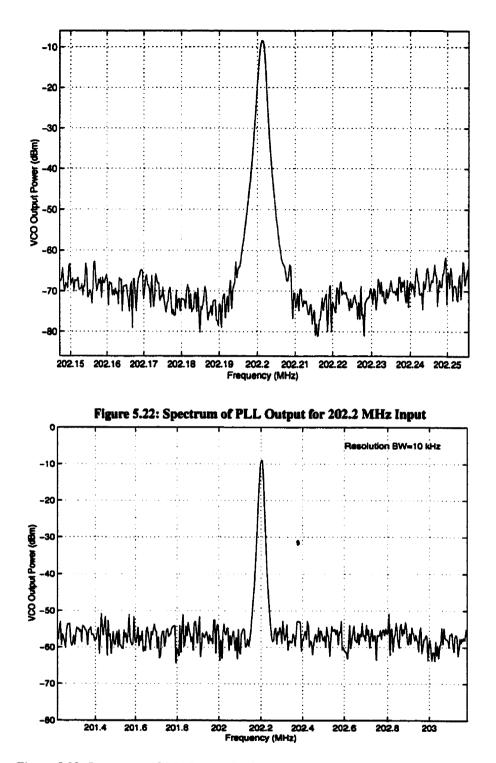

| Figure 5.22: Spectrum of PLL Output for 202.2 MHz Input                            | 111        |

| Figure 5.23: Spectrum of PLL Output for Input Frequency of 202.2 MHz (Zoomed Out)  | 111        |

### List of Figures

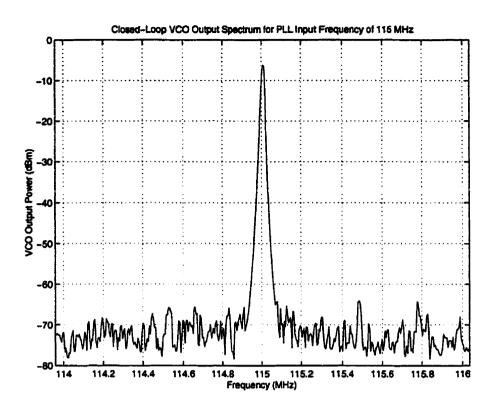

| Figure 5.24: Spectrum of PLL for Input Frequency of 115 MHz (Zoomed Out)                | 112 |

|-----------------------------------------------------------------------------------------|-----|

|                                                                                         |     |

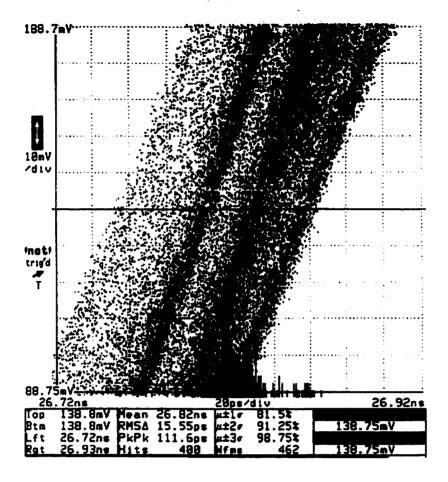

| Figure 5.25: Jitter Histogram of PLL Output at 290 MHz                                  | 113 |

| Figure 5.26: Setup For Measuring Transistor Transconductance                            | 114 |

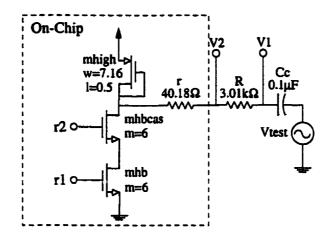

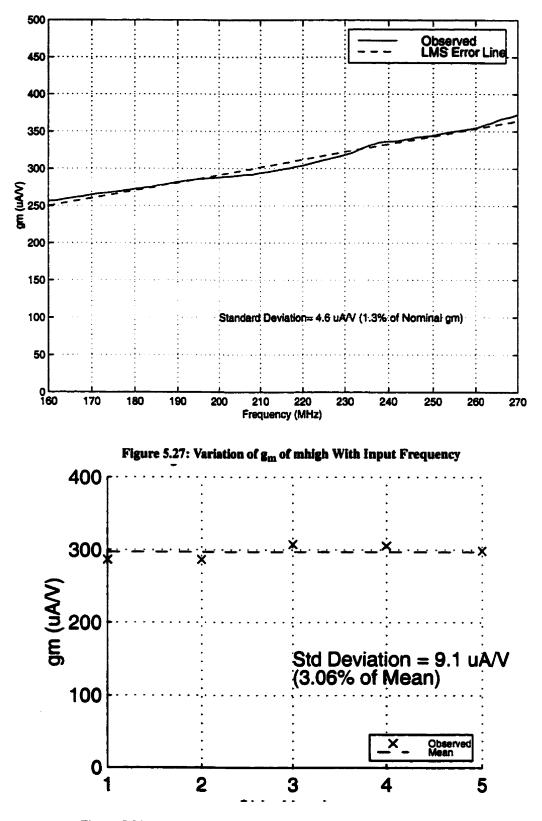

| Figure 5.27: Variation of g <sub>m</sub> of mhigh With Input Frequency                  | 115 |

| Figure 5.28: Variation of g <sub>m</sub> of mhigh Over Process for 5 Chips at 250 MHz   | 115 |

| Figure 5.29: Variation of g <sub>m</sub> of mhigh With Power Supply Voltage at 250 MHz  | 116 |

| Figure 5.30: Transistor g <sub>m</sub> Versus Temperature at a VCO Frequency of 250 MHz | 117 |

| Figure 5.31: Output of DAC 2 Versus Time for Input Signal of 200 MHz                    | 118 |

| Figure 5.32: VCO Frequency Characteristic                                               | 118 |

| Figure 5.33: VCO Characteristic for Fixed Value of V <sub>a</sub>                       | 119 |

| Figure 5.34: VCO Frequency Versus V <sub>a</sub> for Various Digital States             | 120 |

## **Appendix B: Derivation of Inverter Delay**

| Figure B.1: Circuit Schematic For Analyzed Inverter Structure      | 128 |

|--------------------------------------------------------------------|-----|

| Figure B.2: Simplified Circuit Schematic for Falling Output Signal | 129 |

#### **Chapter 1: Introduction**

# Introduction

This chapter presents the motivation behind this design, as well as a description of the target application.

## **1.1 Generation of Accurate Transistor Transconductance**

This section presents a motivation as to why accurate on-chip transistor transconductances are required in general circuit design, and what problems this imposes on the integratedcircuit designer. Next, a possible solution called the constant-transconductance bias circuit [Johns, 1997] is described, along with its problems. Finally, the proposed method of generating accurate transconductances is described.

### **1.1.1 Motivation and Design Implications**

Time-constants are vital quantities in almost every area of circuit design. They determine rise and fall times in digital circuits, and bandwidth in analog circuits. In general, however, these quantities cannot be tightly controlled by the designer due to process variations in the technology used to manufacture the integrated circuits. As a result, important aspects of system performance can vary with the process variations.

Most important time-constants are proportional to  $C/g_m$ , where C is some on-chip capacitance (intentional or parasitic), and  $g_m$  is the transconductance of a transistor. In most technologies, on-chip capacitors can be implemented with relatively high accuracy (3 $\sigma$  variation of

about 10%). Thus, the most important step towards generating well-known accurate time-constants is to ensure that transistor transconductances remain accurately known.

### 1.1.2 Constant-Transconductance Bias Circuit

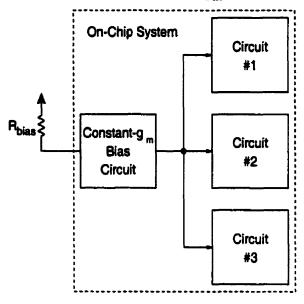

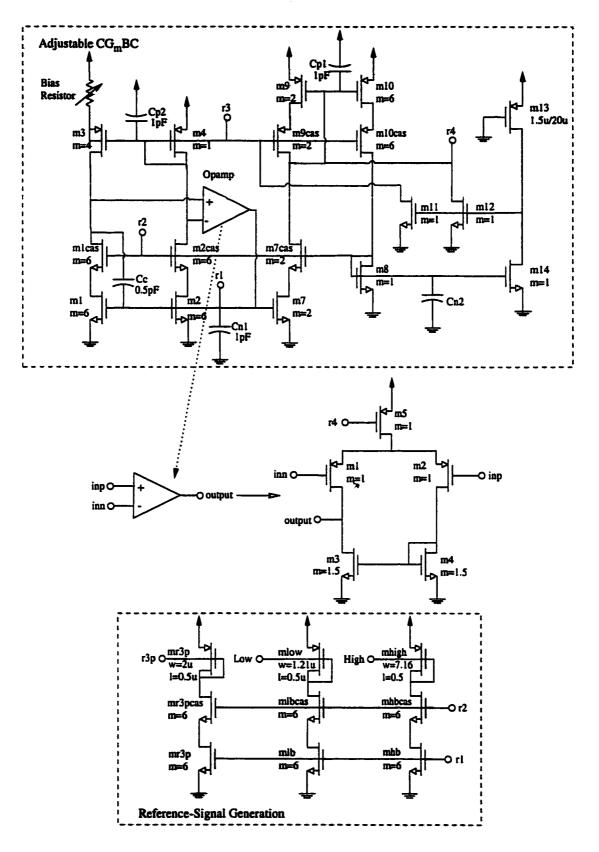

The current design attempts to produce well-known transistor transconductances by building on a circuit called the constant-transconductance bias circuit [Johns, 1997], which in turn was based on a concept found in [Steininger, 1990]. The main idea behind the constant-transconductance bias circuit is outlined in Figure 1.1. In this figure, the subcircuits in the on-chip system are all biased by one or more voltages from the constant- $g_m$  bias circuit (which is also on-chip).

Figure 1.1: Simplified Schematic of Constant-Transconductance Bias Circuit

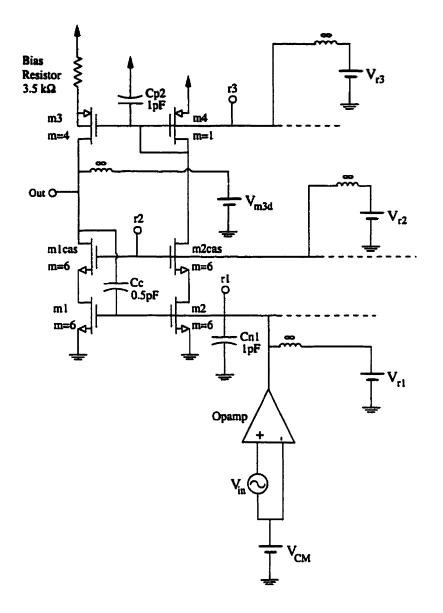

The constant- $g_m$  bias circuit is designed so that the transconductance of transistors it biases are all proportional to the conductance of  $R_{bias}$ . If  $R_{bias}$  is a high-quality surface-mount resistor, then the transconductance of all transistors in the on-chip system will be accurately controlled over process and temperature variations. A problem with this scheme is that the presence of an off-chip resistor  $R_{bias}$  prevents the design in question from being fully integrated. While the resistor could be placed on-chip, this would defeat the purpose of the circuit, as the process variations on  $R_{bias}$  would cause 30% variations in the transconductances realized. Also, it has been found that, in practice, a part of  $R_{bias}$  must be placed on-chip to prevent oscillations in the bias circuit [Cheng,

1998]. This compromises the accuracy of  $R_{bias}$ , so that the accuracy of the transconductances is also compromised, unless the off-chip resistor is tuned during testing.

### 1.1.3 Constant-gm Bias Circuit With PLL-Tuned Resistor

100

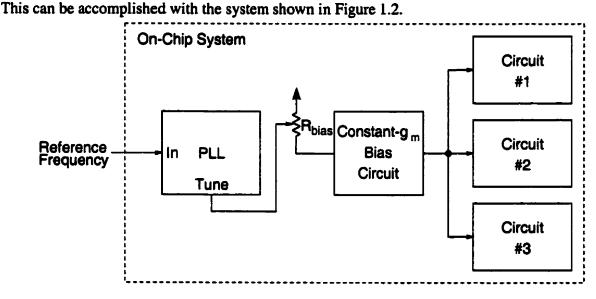

The main disadvantage of the constant- $g_m$  bias circuit is that the bias resistor  $R_{bias}$  must be placed off-chip in order for its value to be sufficiently accurate. To get around this problem, we are proposing to *tune* the bias resistor  $R_{bias}$  so that its value is always well-determined. This can be accomplished with the custom shown in Figure 1.2

Figure 1.2: Simplified Schematic for Proposed System

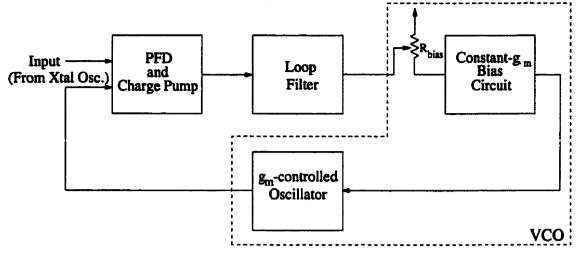

In order to tune the bias resistor, an on-chip PLL is added, which locks to an off-chip crystal oscillator, which would be present anyway in most systems to produce a system clock. Hence, the circuit requires no additional off-chip components than those that would be required anyway in most systems. To ensure that the bias resistor  $R_{bias}$  in Figure 1.2 is always tuned to the same value over process and temperature, the PLL uses the structure shown in Figure 1.3. As can be seen, the VCO for the PLL is comprised of the constant- $g_m$  bias circuit with a tunable resistor that controls the frequency of oscillation of a  $g_m$ -controlled oscillator. In order for the PLL to lock to the input signal from the crystal oscillator, it must adjust the frequency of the VCO to be the same as that of the input. However, in order to do this, the transconductance provided by the bias circuit must be equal to a specific well-determined value. Since the transconductance pro-

vided by the bias circuit is inversely proportional to the bias resistor value, the final value of  $R_{bias}$  will be well-determined over process and temperature as well.

To reduce noise on the bias voltages produced by the bias circuit in Figure 1.2, the PLL uses both digital and analog signals to tune the bias circuit of Figure 1.3. The digital signals are used to change R in medium and large-sized steps, while the analog voltage is used only for fine-tuning. Thus, the resistance R is tuned to approximately the correct value by the digital signals alone, so that in steady-state only the analog control-voltage is active (unless the temperature changes substantially, which usually occurs only slowly). The noise due to ripple on the analog control voltage can be removed by using a second adjustable bias circuit controlled only by the digital signals from the PLL. Assuming the temperature varies slowly, changes to the digital tuning signals will seldom be required (since the crystal frequency remains virtually constant over time). Thus, the system is biased by constant voltages with very little noise on them, as desired.

## **1.2 Intended Application: Wireless Data Communications Receiver**

The intended application for this circuit is to produce the in-phase and quadrature phase 250-MHz IF carriers for a low-cost wireless receiver for the ISM Band, as shown in Figure 1.4. The signals of interest are highlighted in Figure 1.4 by the dotted rectangle. It is immediately obvious that in this application, the biasing scheme chosen has the added benefit that the PLL used to tune the bias resistor can also be used to synthesize the IF carriers. Also, the absence of

-4-

any off-chip components (aside from the crystal oscillator) help to make the system less expensive. It should also be noted that quadrature carriers need to be generated by the PLL.

Figure 1.4: System Schematic for Low-Cost Wireless Receiver

## **1.3 Outline of Thesis**

Chapter 2 contains a background on PLL circuitry and architectures, and introduces the basic design formulae used in designing PLL's. Chapter 3 describes the system-level modelling that was done for this design using SIMULINK, including descriptions of the models, as well as simulation results. Chapter 4 describes the transistor-level circuit design of the various blocks in the system. Chapter 5 describes the testing of the manufactured chips, including test setups and results. Finally, Chapter 6 presents the conclusions for the project.

## **1.4 References**

D. Johns, K. Martin, Analog Integrated Circuit Design. Toronto: John Wiley & Sons, 1997.J. M.

Steininger, "Understanding Wide-Band MOS Transistors," *IEEE Circuits and Devices*, Vol. 6, No. 3, pp. 26-31, May 1990.

J. S. Cheng, "Adaptive Equalization System for Data Transmission over Coaxial Cables," University of Toronto Master's Thesis, 1998.

# Phase-Locked Loops: A Background

This chapter is devoted to reviewing the basic theory behind phase-locked loops. Most of this theory is well understood, and is covered extensively in several textbooks [Gardner, 1979][Wolaver, 1991][Best,1997][Johns, 1997][Encinas, 1993]. The discussion begins with a general description of charge-pump phase-locked loops (PLL's), followed by an overview of the various circuits often used to implement the blocks in a charge-pump PLL. Finally, the important design trade-offs that exist in a charge-pump PLL system are described.

## **2.1 Basic Loop Structure**

The architecture for a charge-pump PLL will now be described, and the equations governing its operation will be derived.

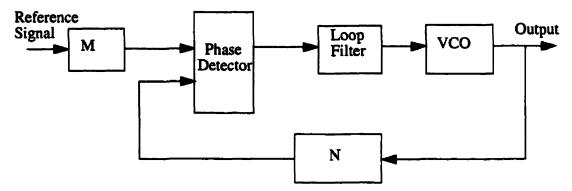

#### 2.1.1 Block Diagram

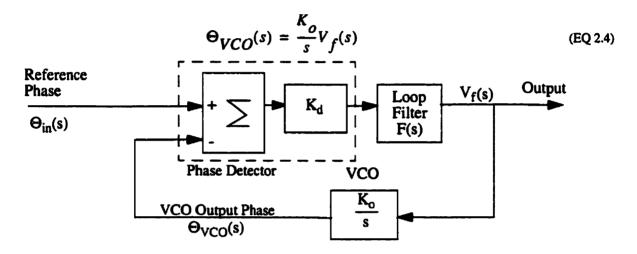

The block diagram for a general PLL is given in Figure 2.1. The phase-detector (PD) senses the phase-difference between the reference and the voltage-controlled oscillator (VCO) signal, and outputs a voltage whose average is proportional to this phase difference. The low-pass loop-filter extracts this average from the PD output. This average is used to control the VCO, whose output frequency is proportional to its input voltage.

When the loop is in lock, the PD outputs a signal with a nearly constant average, so that the VCO frequency remains constant. If the reference frequency rises in value, the PD will

sense this, causing an increase in the loop-filter output-voltage. This in turn increases the VCO frequency, so that the VCO catches up to the input.

The M and N blocks divide the frequency of their input by M and N, respectively. The N block allows the circuit to tune the VCO output to  $f_{in}$ ,  $2f_{in}$ ,  $3f_{in}$ , etc., where  $f_{in}$  is the frequency of the reference input (after the M block). This is useful in applications where the PLL must lock to several different carriers separated by a fixed channel width. The M block allows a higher frequency crystal oscillator to be used, which can be useful if the required reference frequency is very low (say, below 1 MHz, making a crystal oscillator impractical due to size limitations).

Figure 2.1: Block Diagram for General PLL

#### 2.1.2 Classes of PLL Systems

There are three main types of PLL systems: analog PLL's, hybrid analog/digital PLL's, and all-digital PLL's. As their name implies, analog PLL's contain only analog circuitry. Hybrid analog/digital PLL's contain some digital circuitry (usually just the phase detector), while the rest of the PLL blocks remain analog. Finally, all-digital PLL's are entirely composed of digital circuitry. The following discussion will focus on a specific type of analog/digital PLL's called *charge-pump* PLL's, as that is the architecture used in this work.

### 2.1.3 Linearized Small-Signal Model

Assume that the input to the PLL and output from the VCO are both square waves, and that M and N in Figure 2.1 are both equal to one. In a charge-pump PLL, the phase-detector consists of a charge-pump (a simplified example of which is shown in Figure 2.2) driven by a digital

#### **Chapter 2: Phase-Locked Loops: A Background**

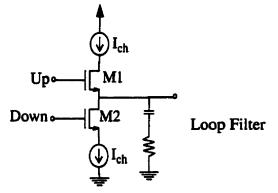

circuit called a phase-frequency detector (PFD). The details of these blocks will be discussed in Section 2.2. The charge-pump adds or removes charge from the loop-filter capacitor under control of the Up and Down signals generated by the PFD. The Up and Down signals are generated such that when the input frequency  $(f_{in})$  is higher than that of the VCO  $(f_{VCO})$ , the Up signal toggles on and off (while the down signal remains low), and when  $f_{in}$  is lower than  $f_{VCO}$ , the Down signal toggles on and off (while the Up signal remains low). When the VCO and input signal are equal in phase and frequency, both Up and Down ideally remain inactive. When the input and VCO have equal frequencies but unequal phase, the duty-cycle of the toggling signal (Up when the input leads the VCO, Down when the input lags the VCO) is proportional to the phase-difference between the input and VCO signals.

Figure 2.2: Simplified Charge-Pump Circuit

To quantify this, the *average* current flowing into the loop-filter capacitor when the PLL is locked can be found to be equal to the expression in Equation 2.1, where  $I_{ch}$  is the charge-pump current in Figure 2.2, and  $\theta_e(t)$  is the phase-error between the input and VCO signals. The constant  $K_d$  is called the phase-detector constant, given in Amperes/radian.

$$I_{avg} = \frac{I_{ch}}{2\pi} \Delta \phi = K_d \theta_e(t)$$

(EQ 2.1)

The phase-detector output is averaged by the loop filter, which controls the VCO. The Laplacedomain loop-filter output-voltage is given in Equation 2.2, where F(s) is the impedance of the loop filter, and  $\Theta_e(s)$  is the frequency-domain phase error between the input and the VCO.

$$V_F(s) = K_d \Theta_e(s) F(s)$$

(EQ 2.2)

Chapter 2: Phase-Locked Loops: A Background

The difference between  $f_{VCO}$  and the free-running VCO frequency is given in the time-domain as in Equation 2.3, where  $v_f(t)$  is the output voltage of the loop filter. Note that when the loop-filter output is zero, the VCO runs at its free-running frequency. The constant  $K_0$  is the VCO gain in

$$\omega_{VCO}(t) = K_o v_f(t) \tag{EQ 2.3}$$

rad/s/Volt. The phase of the VCO output is the integral of this, so that the phase can be expressed in the Laplace domain as in Equation 2.4. The PLL model can therefore be drawn as shown in Figure 2.3.

Figure 2.3: Block Diagram for Linearized PLL

The only major difference between most PLL designs is the implementation of the various blocks in this diagram. Therefore the *general* transfer function of a PLL from the reference phase ( $\Theta_{in}(s)$ ) to the VCO output-phase ( $\Theta_{out}(s)$ ) is given as in Equation 2.5, and the transfer function from  $\Theta_{in}(s)$  to the phase error between the VCO and the reference ( $\Theta_e(s)$ ) is given as in Equation 2.6, where F(s) is the transfer function of the low-pass filter. The loop gain of the PLL is

$$H(s) = \frac{\Theta_{VCO}(s)}{\Theta_{in}(s)} = \frac{K_o K_d F(s)}{s + K_o K_d F(s)}$$

(EQ 2.5)

$$H_e(s) = \frac{\Theta_e(s)}{\Theta_{in}(s)} = \frac{s}{s + K_o K_d F(s)}$$

(EQ 2.6)

defined to be  $K = K_0 K_d F(\infty)$ , so that the high-frequency gain of H(s) can be expressed as K/ (s+K). Thus, the loop gain is also approximately the bandwidth of the PLL.

If F(s) is a first-order low-pass or lead-lag filter, then the denominator of H(s) will be second order, and can be expressed in the form of Equation 2.7, where Q is the quality factor for

$$D(s) = 1 + \frac{s}{\omega_n Q} + \frac{s^2}{\omega_n^2}$$

(EQ 2.7)

the PLL, and  $\omega_n$  is the natural frequency. These values are very important in the design of the loop, in that they determine the settling behaviour of the loop, as will be discussed in Sections 2.3.1 and 2.3.2.

Finally, let us use the final-value theorem to determine the steady-state phase-error for a phase-error and frequency-error step on the PLL input. The phase error as time approaches infinity is given in Equation 2.8, where n=1 for a phase-error step, and n=2 for a frequency error step. Hence, the steady-state phase error is zero for a PLL, provided that the loop-filter transfer

$$\lim_{t \to \infty} \phi_e(t) = \lim_{s \to 0} \frac{1}{o_s^{n-1}} \Theta_e(s) = \lim_{s \to 0} \frac{1}{o_s^{n-1}} \cdot \frac{s}{s + K_o K_d F(s)}$$

(EQ 2.8)

function does not have a zero at DC (a condition that is satisfied for all popular designs). However, in order to achieve zero steady-state phase-error in response to a frequency-error step, the loop-filter must have at least one pole at DC (i.e. it must contain an ideal integrator). It will be seen later that this DC pole can be produced using very simple passive circuitry if a charge-pump architecture is used.

#### 2.1.4 Lock Metrics

The acquisition of lock is the process by which the PLL aligns itself to its input signal, starting from an unlocked state. This section provides definitions for the various metrics used to describe the locking performance of a PLL.

#### 2.1.4.1 Lock-in Range

The lock-in range is defined as the maximum frequency-difference between the PLL input and the VCO frequency for which lock is attainable within one single beat-note, assuming the PLL is initially unlocked. The lock-in time is the time required for this to happen. For frequency offsets smaller than this, lock-in will occur within one beat-note, while for offsets larger than this, lock-in may occur, but after a longer time.

#### 2.1.4.2 Hold Range

The *hold range* describes the maximum frequency-difference for which the PLL will remain locked, assuming it is initially locked, and that the input frequency changes very slowly (i.e. with a rate of change less than the loop bandwidth of the PLL).

#### 2.1.4.3 Pull-in Range

The *pull-in range* is the maximum frequency-difference for which the PLL can eventually attain lock, assuming it is initially unlocked. This is different from the lock-in range, in that it does not specify how long the process must take. If a frequency falls within the lock-in range, it must fall within the pull-in range, however the converse is not true.

#### 2.1.4.4 Pull-out Range

The *pull-out range* is the largest frequency-step that can be applied to the input of the PLL without losing lock, assuming the PLL is initially locked. To remain in lock, all frequency steps must remain smaller than this value, and additionally, there is usually a maximum allowable rate of change for this frequency-step for the PLL to maintain lock.

### **2.2 Block Realizations**

The most common circuits used to realize the blocks of a charge-pump PLL (phase detector, VCO, and loop filter) will now be explored. The design equations for charge-pump PLL's will then be summarized.

### 2.2.1 Phase-Frequency Detector With Charge-Pump

PLL's using this type of PD are called *charge-pump* PLL's. This type of digital PD consists of two main components: the phase-frequency detector (a digital circuit), followed by a charge pump (an analog circuit).

#### 2.2.1.1 Phase-Frequency Detector

The PFD seems to be the most popular PD in recent literature [von Kaenel, 1996][Sung, 1999][Toifl, 1999][Djahanshahi, 1999][Rhee, 1999][Chang, 1999][Sumi, 1999][Wang, 1998][Wu, 1999][Yang, 1997][Craninckx, 1998][Parker, 1998][Rau, 1997]. It has the desirable characteristic that it gives the PLL an infinite hold range and pull-in range even if a passive first-order loop filter is used. Also, the PFD is insensitive to the duty cycle of the input waves, as it is edge-triggered.

Another advantage of the PFD circuit is that it maintains phase-lock over a large phase-error range (from  $-2\pi$  to  $2\pi$ ) without "slipping", which is twice that for a JK flip-flop, and four times that of the multiplier/XOR gate [Best, 1997].

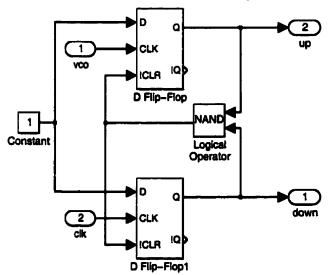

The logical schematic for the circuit is shown in Figure 2.4. To help envision the

Figure 2.4: Schematic for PFD

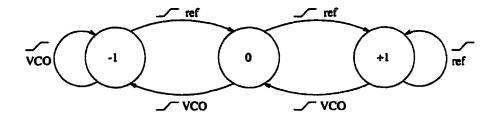

operation of this circuit, refer to the signal-flow graph of Figure 2.5.

Figure 2.5: Signal-Flow Graph for PFD

The circuit changes states only on the positive edges of the input signals. Unless the PLL is in lock, the PFD will alternate between two of the three states. If  $f_{in}$  is larger than  $f_{VCO}$ , the circuit alternates between states 0 and +1, while if  $f_{in}$  is smaller than  $f_{VCO}$ , the circuit alternates between -1 and 0. The state assignments are summarized in Table 2.1.

| State | Up | Down |

|-------|----|------|

| 0     | 0  | 0    |

| +1    | 1  | 0    |

| -1    | 0  | l    |

TABLE 2.1. State Assignment for PFD

The Up and Down outputs control switches that increase or decrease the VCO controlvoltage by adding or removing charge from the loop filter's capacitor, respectively, using the charge-pump. Thus, if  $f_{in}$  is larger than  $f_{VCO}$ , the Up signal will oscillate between 1 and 0, while the down signal will remain at 0. This gradually adds charge to the filter capacitor, which increases the VCO frequency, bringing the PLL closer to lock.

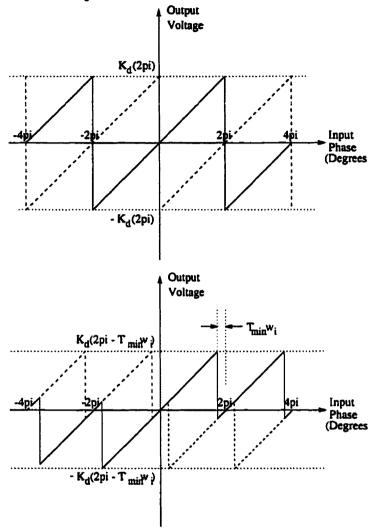

The ideal characteristic for the PFD is shown in Figure 2.6a). In reality, however, the non-zero delay through the flip-flops and NAND gate can alter the characteristic, as seen in Figure 2.6b). To see how this arises, consider the case when the PLL input and VCO output are perfectly in phase. Initially, both PFD outputs are zero. When the first pulse edges arrive at the PFD input, the PFD outputs are forced high. Ideally, this should only occur for an infinitesimal amount of time, however in reality there is a delay through the NAND gate before its output falls to zero, and then another delay through the flip-flops before the low reset signal takes effect at the output. This delay decreases the maximum phase shift that the PFD can handle without slipping. This

maximum phase shift is given by  $\theta_{em} = 2\pi - T_{min}w_i$ , where  $w_i$  is the input frequency in rad/s and  $T_{min}$  is the delay through the NAND and flip-flop [Wolaver, 1991]. Note that as the input frequency increases, the maximum phase decreases.

Figure 2.6: PFD Characteristic: a) Ideal (Upper) b) Non-Zero Delay in Logic (Lower)

#### 2.2.1.2 Charge Pump for PFD

The most basic form of the charge pump was shown in Figure 2.2. The Up and Down signals are provided by the PFD. If the Up signal is raised,  $I_{ch}$  flows into the output node, charging the filter capacitor. If the Down signal is raised,  $I_{ch}$  flows out of the output node, discharging the filter capacitor. In this manner,  $V_{out}$ , which controls the VCO, is changed.

### 2.2.2 Loop Filter

The most common filter used in the literature is the first or second-order passive RC filter, due its simplicity and sufficient performance. The most basic form for this filter is shown in Figure 2.7. This form of the filter is used in analog PLL's and those hybrid analog/digital PLL's in which the PD output signal is a voltage. The transfer function for this circuit is given in Equation 2.9. Note that this loop-filter does not contain an ideal integrator, so that the hold-in and pull-in ranges will be limited. To obtain infinite hold-in and pull-in ranges for analog PLL's (and analog/digital PLL's that don't use a charge-pump structure), one must use a more area and power-hungry active loop-filter.

$$F(s) = \frac{1 + sR_2C_1}{1 + s(R_1 + R_2)C_1}$$

(EQ 2.9)

+  $\frac{R_1}{V_{in}}$  +  $\frac{V_{in}}{R_2}$  +  $V_{out}$

#### Figure 2.7: Lead-Lag Loop Filter

For charge-pump PLL's, a very similar structure is used, however it is excited by current (from the charge-pump) instead of voltage, which changes its transfer function to contain an ideal integrator. Two common realizations for this loop filter are shown in Figure 2.8. In both cases, the capacitor  $C_1$  is usually much larger than  $C_2$ , which is present to suppress glitches across  $R_1$  when current is first switched into the filter.

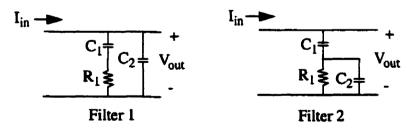

Figure 2.8: Schematic for Lead-Lag Loop Filter for Charge-Pump PLL (Two Realizations)

The transfer function for Filter 1 is given in Equation 2.10, where the approximation holds if  $C_1 >> C_2$ , which is usually the case ( $C_2$  is usually chosen to be at least 10 times smaller

**Chapter 2: Phase-Locked Loops: A Background**

than  $C_1$  [Gardner, 1981]). Notice that the filter contains an ideal integrator, which gives the PLL pull-in and hold-in ranges that are limited by VCO tuning range.

$$F(s) = \frac{1 + sRC_1}{s(C_1 + C_2)\left(1 + s\frac{C_1C_2}{C_1 + C_2}R\right)} \approx \frac{1 + sRC_1}{sC_1(1 + sC_2R)}$$

(EQ 2.10)

The transfer function for Filter 2 is given by Equation 2.11. Notice that both filters are approximately equivalent if  $C_2$  is much smaller than  $C_1$ . Also, note that  $C_2$  has the effect of

$$F(s) = \frac{1 + sR(C_1 + C_2)}{sC_1(1 + sC_2R)} \approx \frac{1 + sR(C_1)}{sC_1(1 + sC_2R)}$$

(EQ 2.11)

introducing a pole at a relatively high frequency, which degrades Q slightly (makes is a little larger). To compensate for this, the filter is often designed ignoring  $C_2$ , but for a lower Q (by about 20%) [Johns, 1997].  $C_2$  makes the loop filter second order, and hence makes the overall PLL third order. Because less understanding exists of third-order systems, the PLL is easier to analyze ignoring  $C_2$ , assuming it only affects the circuit at high frequencies [Gardner, 1980].

### 2.2.3 Voltage-Controlled Oscillator

The three major types of voltage-controlled oscillator (VCO) integrated circuits will now be discussed: LC oscillators, RC multivibrators, and ring oscillators.

#### 2.2.3.1 LC Oscillators

While integration is possible for these circuits, it is very difficult to achieve very high performance on-chip, since high-Q inductors are difficult to create. Also, LC oscillators tend to have fairly narrow tuning ranges.

#### 2.2.3.2 RC Multivibrators

RC multivibrators contain no resonating components, so that their phase-noise performance is inferior to crystal and LC oscillators. However, because they contain no inductors or crystals, these circuits are easily integrated, making them an attractive choice for fully-integrated PLL's. Typically, multivibrator circuits do not have quite as good jitter performance as welldesigned ring oscillator VCO's [Mcneill, 1997].

#### 2.2.3.3 Ring Oscillators

Ring oscillators appear to be the most popular VCO's for fully-integrated CMOS PLL's [Young, 1992][Sung, 1999][Chang, 1999][Rau, 1997][Kim, 1990][Djahanshahi, 1999][Chen, 1999]. Their design is fairly simple and easy to understand, in that they contain n delay elements connected in a series loop. Thus, the period of oscillation is 2nT, where T is the delay of one of the delay elements. For single-ended logic gates, n must be odd in order to make the loop unstable, however if fully-differential logic is used, n can be even, since a sign change can be created by swapping positive and negative outputs to create instability.

Two types of delay elements are commonly used: current-starved elements, and differential inverter elements.

#### **Current-Starved Delay Elements**

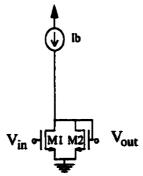

A schematic for a typical current-starved delay element is shown in Figure 2.9 [Yang, 1997]. To see how this delay element works, first assume  $V_{in}$  is high. This means that M2 will be shut off and M1 will conduct  $I_b$ .  $V_{out}$  is then governed by the on-resistance of M1. Next assume  $V_{in}$  is forced low. In this case M1 will shut off, causing  $V_{out}$  to rise to a value determined by the gate voltage of M2. By altering the value of  $I_b$ , the delay through the element can be controlled. In practice, it is better to use a fully-differential version of this circuit [Yang, 1997] in order to reduce the effects of power-supply noise.

Figure 2.9: Schematic for Current-Starved Delay Element

-17-

#### Differential Inverter Delay Elements

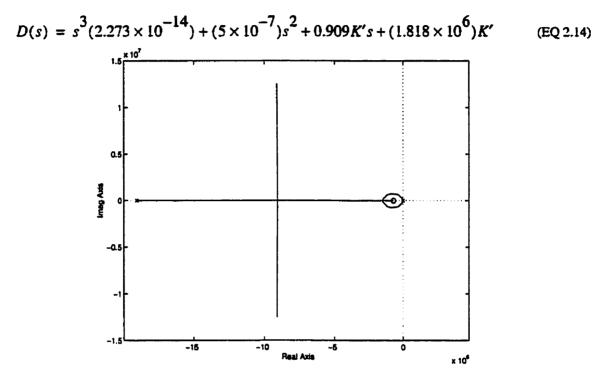

Regular CMOS inverters do not perform well in VCO's because their threshold voltage depends on the power-supply voltage, so that noise on the power-supply creates a large amount of jitter in the VCO's output. To minimize the effects of power-supply noise, fully-differential circuits are used. A typical differential inverter delay-element is shown in Figure 2.10.

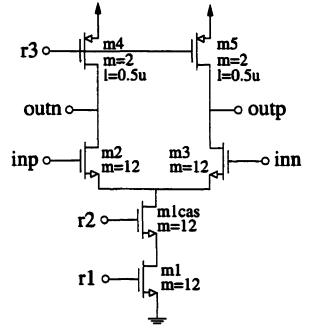

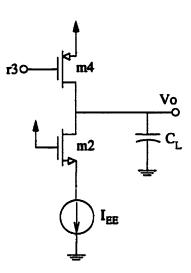

Figure 2.10: Circuit Schematic for Differential Inverter

The input transistors steer the bias current produced by the cascode current-source M1 to either M4 or M5, which are triode-biased PMOS transistors. It can be shown that the delay through the element is approximately  $r_{ds4}C_L ln2$  (see Appendix B). By altering the drain-to-source resistance in M4 and M5, the delay through the element can be controlled, along with the VCO oscillation-frequency.

Like multivibrator circuits, ring oscillators contain no resonant components, which compromises their phase-noise performance. However, this also means that ring oscillators can be easily integrated.

### 2.2.4 Frequency Dividers

As mentioned in Section 2.1.1, frequency dividers are used in some applications. In frequency synthesizers, they are added to generate multiples of the reference frequency, whereas in CPU PLL's, a divide-by-two circuit is usually added after the VCO to help obtain a signal with a 50% duty cycle. The addition of a frequency divider (say, by some integer N) after the VCO lowers the loop bandwidth by a factor N, which degrades the performance (lowers the lock-in

Chapter 2: Phase-Locked Loops: A Background

range and degrades attenuation of VCO phase noise), but also eases the design of the phase detector and charge pump, since they only have to operate at 1/N times the frequency of the VCO.

### 2.2.5 Loop Equations for Charge-Pump PLL With Lead-Lag Loop Filter

The loop equations for a second-order charge-pump PLL with a lead-lag filter are summarized in Table 2.2 (see [Johns, 1997] and [Best, 1997] for derivation). The loop filter structure is assumed to be that of Figure 2.8, in the absence of  $C_2$ . In this table,  $I_{ch}$  is the charge-pump current, R and  $C_1$  are the component values in the loop filter, and  $K_0$  is the VCO gain.

| Quantity                            | Formula                                                                               |

|-------------------------------------|---------------------------------------------------------------------------------------|

| Phase Detector Gain                 | $K_d = \frac{I_{ch}}{2\pi}$                                                           |

| Filter Transfer Function F(s)       | $F(s) = \frac{RC_1 s + 1}{sC_1}$                                                      |

| Natural Frequency (ω <sub>n</sub> ) | $\omega_n = \sqrt{\frac{K_o K_d}{C_1}} \cong \frac{1}{\tau_{PLL}}.$                   |

| Quality Factor                      | $Q = \frac{1}{\omega_n R C_1}$                                                        |

| Transfer Function H(s)              | $H(s) = \frac{1}{K_o} \cdot \frac{s(1 + sRC_1)}{\frac{C_1 s^2}{K_d K_o} + sRC_1 + 1}$ |

| Steady-State Phase Error            | $\theta_{v} = \frac{2\pi\Delta\omega}{K_{o}I_{p}Z_{F}(0)} = 0$                        |

| Lock-in Range                       | $\frac{\pi\omega_n}{2Q}$                                                              |

| Hold Range                          | Infinite (limited by tuning range of VCO)                                             |

| Pull-in Range                       | Infinite (limited by tuning range of VCO)                                             |

TABLE 2.2. Formulae for PFD and Passive Lead-Lag Filter

#### Chapter 2: Phase-Locked Loops: A Background

TABLE 2.2. Formulae for PFD and Passive Lead-Lag Filter

| Quantity       | Formula                                           |

|----------------|---------------------------------------------------|

| Pull-out Range | $11.55\omega_n \left( 0.5 + \frac{1}{2Q} \right)$ |

The natural frequency approximates the inverse of the loop time-constant, assuming a first-order response. Thus, the natural frequency is very important in determining the noise tracking ability of the PLL, as will be discussed in Section 2.3.1.

The hold range and pull-in range of the charge-pump PLL approach infinity, meaning that the PLL can always lock to the input frequency (assuming the VCO does not saturate), and assuming the input frequency doesn't change too quickly, the PLL will remain in lock. This is a direct result of the PFD used in the charge-pump PLL, and is in sharp contrast with other PLL types (e.g. hybrid analog/digital PLL with a flip-flop phase detector, analog PLL), whose hold range and pull-in range are often limited by the phase-detector, and not the VCO tuning range, unless an active loop-filter is used.

### **2.3 Design Issues**

It was decided to use a charge-pump structure for the PLL, using a ring-oscillator VCO. The charge-pump/PFD was chosen as the phase-detector, since it allows a large pull-in and hold-in range, even if a simple passive filter is used. The ring-oscillator was chosen because it allowed the creation of a transconductance-controlled oscillator, as will be discussed in Chapter 4. Some of the more important design issues involved in such a system will now be discussed.

#### 2.3.1 Loop Bandwidth

The loop bandwidth controls several areas of performance. The first is the immunity to input noise. The second is the ability to correct for noise generated in the VCO.

The noise appearing at the input of the PLL sees a low-pass response with a cutoff frequency approximately given by the natural frequency. Thus, decreasing the natural frequency (loop bandwidth) will improve the immunity of the PLL to input noise. If the input signal comes from a high-quality oscillator, then input noise will be of little or no concern.

Phase error in the VCO sees a high-pass transfer function (since the internal phase error sees  $H_e(s)=1$ -H(s), where H(s) is the PLL response from the input phase to the VCO output phase), with a cutoff approximately given by the natural frequency of the PLL [Parker, 1998]. Thus, phase noise generated by the VCO gets attenuated if it is offset from the free-running frequency by less than the natural frequency. Outside of this range, the PLL can no longer correct for the phase error, and the phase noise appears unattenuated at the PLL output. Thus, to "track out" the maximum amount of phase noise from the VCO, one should choose a high bandwidth.

### 2.3.2 Quality Factor and Natural Frequency

The quality (Q) factor should be chosen based on the desired response of the loop. A Q factor of 0.5 gives real poles for H(s). A Q factor of  $\frac{1}{\sqrt{3}}$  gives maximally flat group delay, while a Q factor of  $\frac{1}{\sqrt{2}}$  gives maximally flat amplitude response [Johns, 1997].

#### 2.3.3 PFD

There are several important issues to be considered in the design of a PFD. These include behaviour of the PFD around lock, and the logic family to be used.

#### 2.3.3.1 Lock Behaviour

In a perfect PFD, when the VCO is locked to the PLL input, the Up and Down outputs toggle on and off simultaneously, so that, assuming an ideal charge-pump with equal charging and discharging currents, the net change in the charge stored on the loop filter capacitor remains fixed. This translates to the VCO control-voltage remaining constant in steady-state. However, it is difficult to exactly match the Up and Down currents in the charge-pump under all conditions, so that the charge on the loop-filter capacitor is altered if the Up and Down outputs of the PFD are pulsed simultaneously. This means that the PLL must create a suitable phase-offset between the VCO and PLL input in order to hold the VCO control-voltage constant. In applications where steady-

state phase-alignment of the VCO output and PLL input is important, this problem must be carefully addressed.

#### 2.3.3.2 Logic Family

Similar issues arise in the design of the PFD as those in the frequency divider (see Section 2.2.4). The logic in the PFD must be fast enough to settle within a fraction of a period of the VCO, which demands the use of high-performance logic families (ECL, True Single-Phase). The design should also reject power-supply noise, which again suggests using differential logic.

#### 2.3.4 Charge-Pump

A great number of charge-pump circuits have been proposed in the literature. This section sums up the main issues to be considered in the design of a charge pump.

#### 2.3.4.1 Up/Down Symmetry

The transient responses for the up and down currents in the charge-pump must be as well matched as possible, so that equal-duration up and down voltage pulses result in the same change of charge on the loop-filter capacitor. This is especially important once the loop is locked in, since if the up and down transients significantly differ, the short equilength up/down pulses at the output of the PFD will result in a net removal or addition of charge over a long period of time, resulting in a steady-state phase-offset between the VCO and input signal (which may or may not be important, depending on the application)

#### 2.3.4.2 Variation of Up/Down Currents

If single-transistor current sources are used for the simple charge pump in Figure 2.2, the current supplied by them will vary considerably as the charge pump output-voltage changes, due to the small output-resistance of these current sources. To decrease this variation, the output resistance of these sources can be boosted using cascode current-sources.

## 2.3.5 VCO

The VCO is a block that has received a great deal of attention in the literature, since a stable, high-quality, low phase-noise VCO is very difficult to achieve on-chip. Besides the obvious speed and tunability requirements, the main issues in the design are jitter and the linearity of the frequency versus control-voltage characteristic.

#### 2.3.5.1 Jitter

The jitter of the VCO can be an extremely important factor in the determination of the output jitter of the PLL. This is especially true if the input signal has very little jitter. Note also that VCO jitter considerations are only worthwhile if power-supply noise has been dealt with properly (e.g. by using a fully-differential architecture, large decoupling capacitors on the VCO power supplies, and separate power supplies for digital and analog circuitry). If this is not the case, power-supply noise will likely dominate the performance [Martin, 1999].

For a good discussion of timing jitter in CMOS ring oscillators, see [Welgandt, 1998]. However, substitute the expression given for the delay per stage with that used in Mcneill's paper, which is RC<sub>L</sub>ln2. This yields a normalized (to the delay per stage) timing-jitter per stage as given in Equation 2.12 [Martin, 1999]. For the overall oscillator,  $T_{osc}=2nt_d$ , and from the central limit theorem,  $\Delta T_{osc}^2 = 2n\Delta t_d^2$ , which gives the expression for the normalized VCO jitter given in Equation 2.13.

$$\frac{\Delta t_d^2}{t_d^2} = \frac{2.8kT}{Vpp^2 C_L} \left(1 + \frac{2}{3}A_v\right) = \frac{2.8kT}{Vppt_d I_{DD}} \left(1 + \frac{2}{3}A_v\right)$$

(EQ 2.12)

$$\frac{\Delta T_{osc}}{T_{osc}^{2}} = \frac{1.4kT}{nVppt_{d}I_{DD}} \left(1 + \frac{2}{3}A_{\nu}\right) = \frac{1.4kTF_{osc}}{VppI_{DD}} \left(1 + \frac{2}{3}A_{\nu}\right)$$

(EQ 2.13)

Equation 2.13 helps to establish some guidelines in the design of low-jitter ring oscillators. The first is that the gain of the inverters should not be excessive. A minimum value of 1 is required to start oscillations in the circuit, however increasing the gain increases the jitter, so the

#### **Chapter 2: Phase-Locked Loops: A Background**

gain should not be made any larger than necessary. The second guideline is that the power dissipated in the load devices should be maintained as high as possible. Lastly, note that as the frequency of oscillation increases, the jitter increases. This is because a given amount of jitter will have a larger effect on the frequency of oscillation as the period of oscillation gets smaller.

#### 2.3.5.2 Frequency-Control Voltage Characteristic

In order to maintain constant loop dynamics (i.e. Q and  $\omega_0$ ), it is usually desired to keep the VCO gain constant, which implies a linear frequency-control voltage characteristic.

### 2.3.6 Integration of Loop Filter

When designing the PLL, quantities must be chosen such that the loop filter components are realizable on-chip. This means that the filter capacitor must be chosen to be a couple hundred pF at the most (the largest size found in the literature for a 0.35  $\mu$ m CMOS technology is 250 pF in [Djahanshahi, 1999]).

#### 2.3.7 Loop Gain

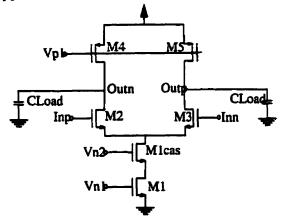

The loop gain is defined as the gain around the loop at high frequencies, which can be found to be  $K_0K_dR$ . To look at stability requirements for the PLL, one can look at the root locus plot. To do this, one can define the normalized loop gain, which is the regular loop gain multiplied by RC<sub>1</sub>. [Gardner, 1980]. Using the parameter values given in Table 2.3, and using the H(s)

| Parameter      | Value                        |

|----------------|------------------------------|

| R              | 18.26 Kilo-ohms              |

| C <sub>i</sub> | 75pF                         |

| C <sub>2</sub> | 3pF                          |

| Ko             | 15.7X10 <sup>6</sup> rad/s/V |

| K <sub>d</sub> | 15.92X10 <sup>-6</sup> V/rad |

| I <sub>b</sub> | 100uA                        |

| Q              | 0.4                          |

12

**TABLE 2.3. Parameter Values Used for Root Locus Plot**

| Parameter      | Value  |

|----------------|--------|

| f <sub>o</sub> | 291kHz |

expression given in [Gardner, 1980], the expression in Equation 2.14 was found for the denominator of H(s), where K' is the normalized loop gain of the PLL.

Figure 2.11: Root Locus Plot for Third-Order System

The root locus plot for such a system is given in Figure 2.11. Note that for all K'>0, the system is stable, since all poles lie in the left-half plane. For small values of K', the system is underdamped with 2 complex poles and one (large) real pole. If K' is increased from this value, the system becomes overdamped with all real poles. Once K' is increased beyond a certain value, however, two of the poles become complex, and the system again becomes underdamped. Thus there is a range of K' for which the system will be overdamped.

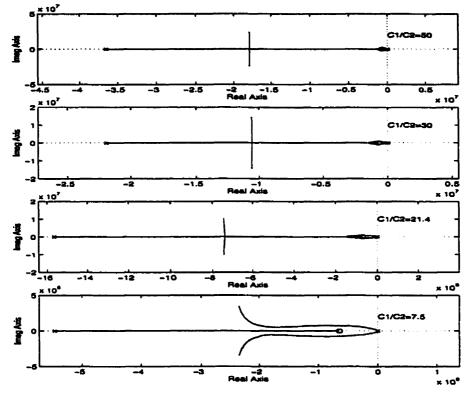

As the ratio of  $C_1/C_2$  is increased by decreasing  $C_2$ , the breakaway point moves further into the left-half plane. In fact, if  $C_1/C_2$  is less than 8, then the system is underdamped for *all* values of K', since the root locus never returns to the real axis after breaking from the origin [Gardner, 1980]. This is verified in Figure 2.12, which shows the root loci of the PLL for varying values of  $C_1/C_2$ . Notice that as this ratio decreases from the initial value of 50, the breakaway point for the poles moves closer to the origin. Finally, for  $C_1/C_2=7.5$ , the poles are complex for all values of loop gain, as expected.

Figure 2.12: Behaviour of Root Loci for Varying Values of C1/C2

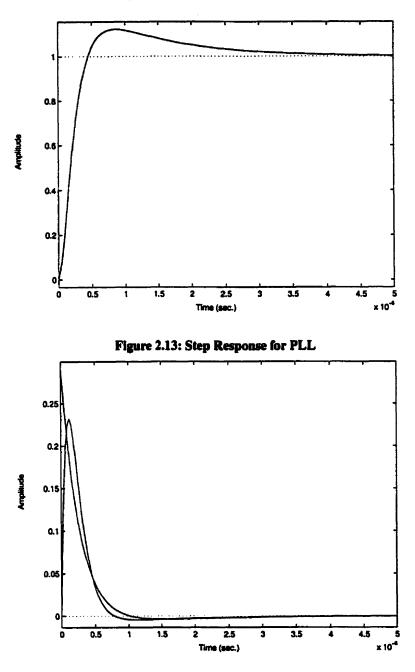

To confirm the system response, the step response was found for the overall PLL, and is plotted in Figure 2.13. The step response for the PLL taken at the input to the VCO is shown in Figure 2.14, along with the step response of the system without capacitor  $C_2$ . As expected, with  $C_2$  included, the voltage rises and then falls to zero as the system comes back into phase with the reference, although there is a slight overshoot in returning to zero. The presence of  $C_2$  removes the step that occurs at the start of the response, so that the VCO input displays a more gradual rise in voltage.

Figure 2.14: Step Response of PLL at Input to VCO

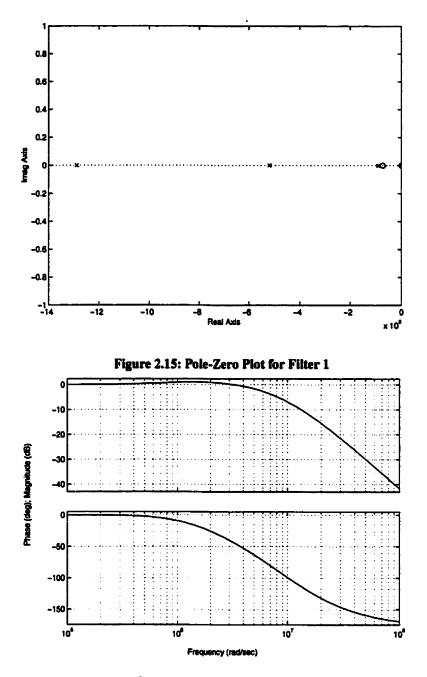

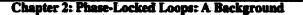

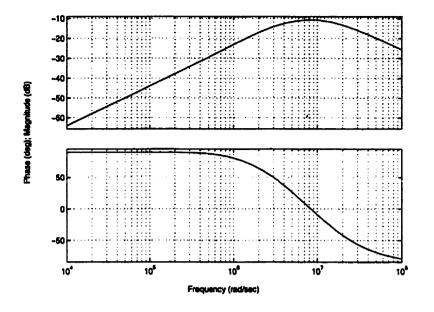

Finally, the pole-zero plot for the PLL with Filter 1 is shown in Figure 2.15. Notice that the low-frequency pole is actually cancelled by the zero introduced by the filter. Thus, the system approximately looks like a second order system with two real poles and no zeros. This is illustrated in Figure 2.16, which is a Bode plot of the PLL with Filter 1. The response is almost flat up to 10Grad/s (1.6 GHz), and then starts to fall off at -40dB per decade.

Figure 2.16: Bode Plot for PLL With Filter 1

It is also interesting to see the system response at the input to the VCO. This is shown in Figure 2.17. As can be seen, the system is bandpass with a very narrow passband centered around 8.5Mrad/s (1.35 MHz).

Figure 2.17: Bode Plot of PLL at Input to VCO

## **2.4 References**

R.E. Best, Phase-Locked Loops, 3rd Ed. Toronto: McGraw-Hill, 1997.

Y. Chang, E.W. Greeneich, "A Current-Controlled Oscillator Coarse-Steering Acquisition-Aid for High Frequency SOI CMOS PLL Circuits," *ISCAS*, Vol. II, pp. 561-564, 1999.

H. Chen, E. Lee, R. Geiger, "A 2-GHz VCO With Process and Temperature Compensation," *ISCAS*, Vol. II, pp. 569-572, 1999.

J. Craninckx, M. Steyaert, "A Fully Integrated CMOS DCS-1800 Frequency Synthesizer," *IEEE ISSCC*, Session 23.5, 1998.

H. Djahanshahi, C.A.T. Salama, "Differential 0.35um CMOS Circuits for 622MHz/933MHz Monolithic Clock and Data Recovery Applications," *ISCAS*, Vol. II, pp. 93-96, 1999.

J.B. Encinas, Phase Locked Loops, New York: Chapman & Hall, 1993.

F.M. Gardner, Phaselock Techniques, 2nd Ed. Toronto: John Wiley & Sons, 1979.

F.M. Gardner, "Charge-Pump Phase-Lock Loops," *IEEE Transactions on Communications*, Vol. COM-28, pp. 1849-1857, 1980.

D. Johns, K. Martin, Analog Integrated Circuit Design. Toronto: John Wiley & Sons, 1997.

B. Kim, D. N. Helman, P.R. Gray, "A 30MHz Hybrid Analog/Digital Clock Recovery Circuit in 2um CMOS," IEEE Journal of Solid-State Circuits, vol. 25, no. 6, pp. 1385-1394, Dec. 1990.

John A. McNeill, "Jitter in Ring Oscillators," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 6, pp. 870-878, June 1997.

K. Martin, PLL Notes, 1999.

J. F. Parker, D. Ray, "A 1.6-GHz CMOS PLL with On-Chip Loop Filter," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 3, pp. 337-343, Mar. 1998.

M. Rau, T. Oberst, R. Lares, A. Rothermel, R. Schweer, and N. Menoux, "Clock/Data Recovery PLL Using Half-Frequency Clock," IEEE Journal of Solid-State Circuits, vol. 32, no. 7, pp. 1156-1159, Jul. 1997.

W. Rhee, "Design of Low-Jitter 1-GHz Phase-Locked Loops for Digital Clock Generation," *ISCAS*, Vol. II, 1999.

Y. Sumi, S. Obote, N. Kitai, R. Furuhashi, Y. Matsuda, Y. Fukui, "PLL Frequency Synthesizer with an Auxiliary Programmable Divider," *ISCAS*, Vol. II, pp. 532-536, 1999.

H. Sung, K.S. Yoon, "A 3.3-V High-Speed CMOS PLL With 3-250 MHz Input Locking Range," ISCAS, Vol. II, pp. 553-556, 1999.

T. Toifl, P. Moreira, "A Radiation-Hard 80-MHz Phase-Locked Loop for Clock and Data Recovery," *ISCAS*, Vol. II, pp. 524-527, 1999.

V. von Kaenel, D. Aebischer, C. Piguet, and E. Dijkstra, "A 320-MHz, 1.5 mW @ 1.35 V CMOS PLL for Microprocessor Clock Generation," *IEEE J. Solid-State Circuits*, Vol. 31, No. 11, pp. 1715-1722, Nov. 1996.

C. Wang, Y. Chien, Y. Chen, "A Practical Load-Optimized VCO Design for Low-Jitter 5V 500-MHz Digital Phase-Locked Loop," *ISCAS*, Vol. II, pp. 528-531, 1998.

T. C. Welgandt, B. Kim, P.R. Gray, "Analysis of Timing Jitter in CMOS Ring Oscillators,"

Dan H. Wolaver, Phase-Locked Loop Circuit Design. Toronto: Prentice-Hall, 1991.

L. Wu, H. Chen, S. Nagavarapu, R. Geiger, E. Lee, W. Black, "A Monolithic 1.25 GBits/s CMOS Clock/Data Recovery Circuit for Fibre Channel Transceiver," ISCAS, Vol. II, pp. 565-568, 1999.

H.C. Yang, L.K. Lee, R.S. Co, "A Low Jitter 0.3-165 MHz CMOS PLL Frequency Synthesizer for 3 V/5 V Operation," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 4, pp. 582-586, Apr. 1997.

I. A. Young, J. K. Greason, K. L. Wong, "PLL Clock Generator With 5 to 110 MHz of Lock Range," *IEEE J. Solid-State Circuits*, vol. 27, no. 11, pp. 1601-1604, Nov. 1992.

# Block-Level Modeling and Design

With an understanding of the general structure of PLL's, it is now possible to examine the new architecture used in this design. In this chapter, this structure is described, as well as the high-level block selection and SIMULINK simulation of the system. Section 3.1 justifies the usage of SIMULINK models. Section 3.2 gives the block-level description of the PLL design. Section 3.3 describes the high-level selection and design of the system blocks. Section 3.4 describes the SIMULINK system used to model the behaviour of the PLL. Finally, Section 3.5 describes the results obtained from the SIMULINK system.

# **3.1 PLL Simulation Problems**

It is well-known that, in general, PLL's are very difficult to simulate at the transistorlevel using a circuit simulator such as HSPICE, since they contain a very wide range of time-constants. Very large time-constants (on the same order as the PLL  $1/\omega_0$ ) are induced by the loop filter, while much smaller time-constants are present in the VCO (often less than one ten-thousandth of the PLL  $1/\omega_0$ ). Hence, the PLL must be simulated using a very small time-step to get accurate results, but also for a very long time-period in order to observe the behaviour of the overall PLL system. At the current time, this places unreasonable requirements on computer memory and time, unless extremely simple circuitry is used [Razavi, 1997].

While long simulations may be acceptable if one is reasonably sure that the design will work, they make design iterations extremely long. As an alternative to long, memory-hungry

transistor-level simulations, the designer may initially verify the system design using a simplified model. If the designer can then design circuits to imitate the behaviour of the simplified system blocks, then the interconnection of these blocks is likely to work properly, and can be verified with a few long transistor-level simulations.

The system-level simulations for this design were carried out using SIMULINK, with the help of C MEX Files [Math Works, 1996]. A good source for understanding how to apply C MEX files to PLL systems is in [Johns, 1997].

## **3.2 System Block-Level Description**

The system will now be described at the block level, followed by a discussion of the advantages of this system design.

## **3.2.1 System Description**

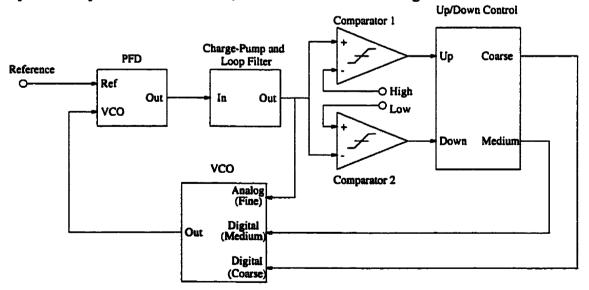

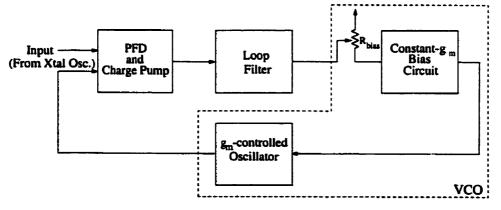

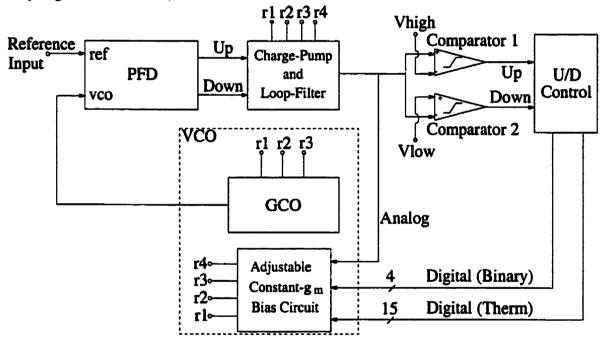

The block diagram for the system is given in Figure 3.1. Relating back to the block diagram of Figure 2.1, the blocks in Figure 3.1 can be lumped together as follows: the phase-frequency detector (PFD) and charge pump blocks form the phase detector block in Figure 2.1, the loop filter block is the same as the loop filter block in Figure 2.1, and the rest of the circuitry (comparators, Up/Down Control, VCO) forms the VCO block of Figure 2.1.

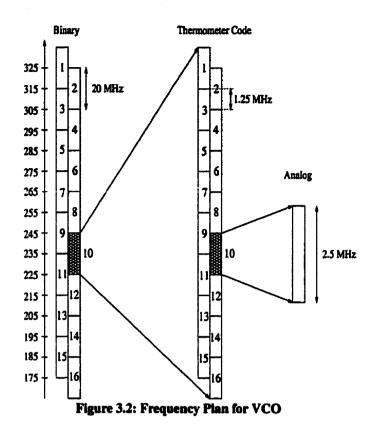

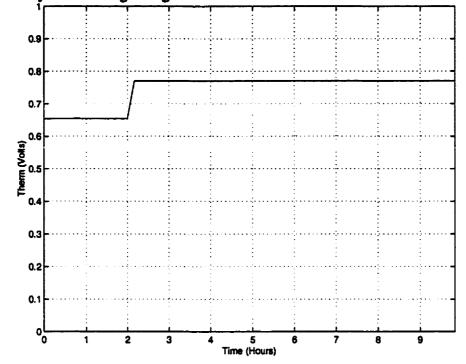

The VCO structure is the most significant aspect of the system, as the other blocks are fairly conventional, being present in almost all charge-pump PLL's [Von Kaenel, 1996][Young, 1992][Parker, 1998][Rau, 1997][Nati, 1997]. The VCO differs from conventional VCO's in that it takes three control inputs, instead of just one. As seen in Figure 3.1, the three VCO inputs correspond to three levels of control resolution. An analog control voltage  $(V_a)$  is used for fine-tuning of the VCO frequency, while two separate digital voltages are used to tune the VCO in medium-sized and large-sized steps ( $V_{therm}$  and  $V_{biny}$  respectively).