# **NOTE TO USERS**

Page(s) not included in the original manuscript are unavailable from the author or university. The manuscript was microfilmed as received.

> 45 and 46 (Section 3.2.2)

This reproduction is the best copy available.

# UMI

# CMOS Compatible Power MOSFETs for On-Chip DC/DC Converters

by Sameh G. Nassif-Khalil

A thesis submitted in conformity with the requirements for the Degree of Master of Applied Science Department of Electrical and Computer Engineering University of Toronto 1999

© Copyright by Sameh G. Nassif-Khalil 1999

#### National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your ille Votre rélérance

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-50383-6

# Canadä

# CMOS Compatible Power MOSFETs for On-Chip DC/DC Converters

Master of Applied Science, 1999 Sameh G. Nassif-Khalil Department of Electrical and Computer Engineering University of Toronto

## Abstract

This thesis deals with low-voltage power MOSFETs which are used in portable, highefficiency switch mode DC/DC converters for personal digital assistants (PDA's) applications. Two power MOSFETs based on lateral, low-voltage CMOS processes and capable of carrying 1 A of current in the on-state are investigated in this thesis.

The first device uses a 0.8  $\mu$ m single level metallization CMOS process. The unit cell pitch of the MOSFET switch is 4.1  $\mu$ m using a channel length of 0.8  $\mu$ m. The layout of a power switch with 1 A current carrying capability uses a checkerboard pattern to maximize the channel width per unit area resulting in a total active chip area of 290×290  $\mu$ m<sup>2</sup> corresponding to a total channel width of 31,878  $\mu$ m. Simulations results of the unit cell show that a specific on-resistance of 117.46  $\mu$ Ω.cm<sup>2</sup>, device on-resistance of 90.1 mΩ and total gate charge of 0.34 nC can be achieved.

The second device uses a 0.25  $\mu$ m - 5 level metallization commercial CMOS process. Experimental results for the 0.25  $\mu$ m switch show significant performance improvement over the 0.8  $\mu$ m design. A specific on-resistance of 6.822  $\mu$ Ω.cm<sup>2</sup> is achieved using a cell pitch of 1.85  $\mu$ m. The layout of the switch utilizes a checkerboard pattern resulting in an active chip area of 130×130  $\mu$ m<sup>2</sup> corresponding to a total channel width of 12,499  $\mu$ m. Experimental results also show that the switch achieves a rise and fall time of 5.8 and 3.5 ns, respectively, an on-resistance of 40.37 mΩ and a total gate charge of 0.105 nC.

ii

### Acknowledgments

I would like to express my sincere appreciation and gratitude to Professor C. A. T. Salama for his insightful guidance, encouragement and support throughout the course of this work.

My thanks to the clean room staff: Dod Chettiar, Dana Reem and Richard Barber for their technical assistance and cooperation. Assistance from Jaro Pristupa in numerous occasions (not only in software) deserves special thanks. Also thanks to Professor Wai Tung Ng for his insightful advice.

I would like to thank my friends Shahla Honarkhah and Sotoudeh Hamedi-Hagh for very valuable discussions and advice both technically and personally.

My appreciation is extended to every member of the Integrated Circuit Laboratory for a very pleasant working environment. Thanks go to Naoto Fujishima, Diana Gradinaru, Jeewika Ranaweera, Mehrdad Ramezani and Dusan Suvakovic. My thanks also go to my friend Monica Bettich.

Financial support provided by the Natural Sciences and Engineering Research Council of Canada, MICRONET, Gennum Corporation, Mitel, and Nortel is greatly appreciated.

Last, but not least, I would like to especially thank my mother and my sister for their love and support and to take this opportunity to dedicate this thesis to my father whose devotion and support throughout the years deserve special acknowledgments and appreciation.

iii

# **Table of Contents**

#### **CHAPTER 1**

| Introduction                                     | 1  |

|--------------------------------------------------|----|

| 1.1 Power Losses in Switch Mode DC/DC Converters | 2  |

| 1.2 Current Status of Power MOSFET Switches      | 5  |

| 1.3 Lateral Power MOSFETs                        | 6  |

| 1.4 Figure Of Merit for Power Switches           | 8  |

| 1.5 Thesis Objective and Organization            | 10 |

| References                                       | 11 |

### **CHAPTER 2**

| 1-A Power MOSFET in 0.8 μm CMOS Technology             |    |

|--------------------------------------------------------|----|

| 2.1 Introduction                                       | 12 |

| 2.2 1-A Power Switch in 0.8-µm CMOS Process            | 12 |

| 2.3 Design Criteria for Low-Voltage Power Switch       | 14 |

| 2.3.1 Specific On-Resistance                           | 14 |

| 2.3.2 Input Capacitance C <sub>iss</sub>               | 16 |

| 2.3.3 Short Channel Effects                            | 17 |

| 2.3.4 Subthreshold Current                             | 18 |

| 2.3.5 Hot Carrier Injection & Parasitic Bipolar Action | 20 |

| 2.4 Process Description                                | 21 |

| 2.5 Layout of 1 A Power Switch                         | 23 |

| 2.6 Process Simulations                                | 29 |

| 2.6.1 2-D Process Simulations Using TSUPREM-4          | 29 |

| 2.7 Device simulations                                 |    |

| 2.7.1 I-V Characteristics                              |    |

| 2.7.2 Charge Transfer Characteristics & FOM            | 36 |

| 2.8 Summary                                            | 39 |

| References                                             | 40 |

#### CHAPTER 3

| 1-A Power MOSFET in 0.25 µm CMOS Technology               | 41 |

|-----------------------------------------------------------|----|

| 3.1 Introduction                                          | 41 |

| 3.2 The 0.25 µm MOSFET Unit Cell                          | 42 |

| 3.2.1 Layout of the 0.25 µm MOSFET Unit Cell              | 44 |

| 3.2.2 I-V Characteristics of the 0.25 µm MOSFET Unit Cell | 45 |

| 3.3 0.25 µm Power MOSFET Switch Layout                    | 47 |

| 3.4 Experimental Results                                  | 49 |

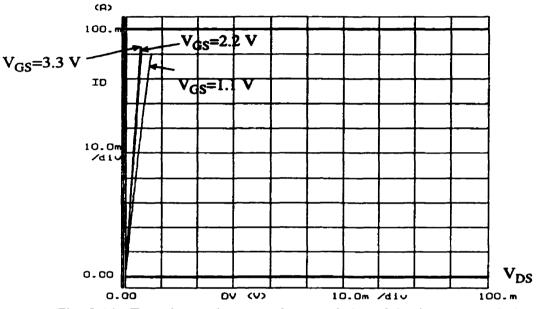

| 3.4.1 Output Characteristics                              | 52 |

| 3.4.2 Transfer Characteristics                            | 52 |

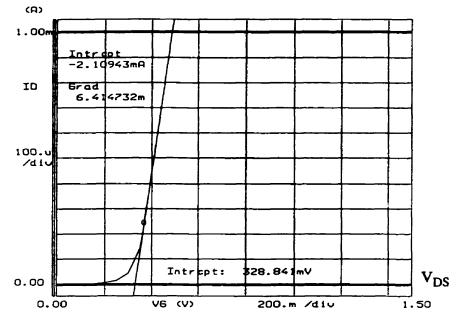

| 3.4.3 Breakdown Voltage (BV <sub>DS</sub> )               | 54 |

| 3.4.4 On-Resistance                                       | 55 |

| 3.4.5 Total Gate Charge Qg and Figure Of Merit (FOM)      | 57 |

| 3.4.6 Rise and Fall Time                                  | 59 |

| 3.5 Summary                                               | 59 |

| References                                                | 61 |

### **CHAPTER 4**

| onclusions |

|------------|

|------------|

#### Appendix A

| Layout Design Rules for the 0.8 | μm Process |

|---------------------------------|------------|

|---------------------------------|------------|

# **List of Figures**

| Pag                                                                                          | e |

|----------------------------------------------------------------------------------------------|---|

| Fig. 1.1: Switch mode DC/DC converter                                                        |   |

| Fig. 1.2: Gate drive equivalent circuit                                                      |   |

| Fig. 1.3: Vertical DMOST cross section                                                       |   |

| Fig. 1.4: TMOST cross section                                                                |   |

| Fig. 1.5: Lateral MOSFET cross section (unit cell)                                           |   |

| Fig. 1.6: Charge transfer characteristics                                                    |   |

| Fig. 1.7: Test circuit for charge transfer characteristics                                   |   |

| Fig. 2.1: Cross section of the 0.8 µm N-channel lateral MOSFET                               |   |

| Fig. 2.2: Cross section of the LDD MOSFET structure indicating different components          |   |

| of the on-resistance                                                                         |   |

| Fig. 2.3: Cross section of the LDD MOSFET indicating various capacitance components          |   |

| in the structure                                                                             |   |

| Fig. 2.4: Effect of $V_t$ scaling on subthreshold leakage current                            |   |

| Fig. 2.5: Parasitic bipolar action in short channel MOSFETs                                  |   |

| Fig. 2.6: 0.8 μm N-channel process flow                                                      |   |

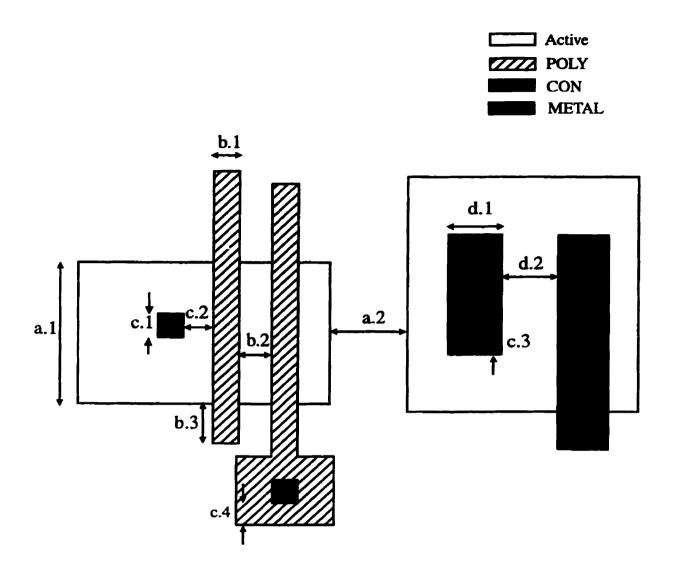

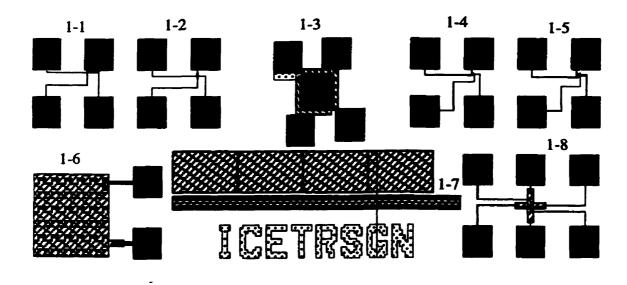

| Fig. 2.7: Checkerboard layout pattern using single level metallization                       |   |

| Fig. 2.8: Device structure (a) top view (b) cross section of the unit cell                   |   |

| Fig. 2.9: Net doping contours of the unit cell                                               |   |

| Fig. 2.10: Simulated doping profiles in (a) S/D region (b) channel region (c) LDD            |   |

| region                                                                                       |   |

| Fig. 2.11: Simulated transfer characteristics of the unit cell                               |   |

| Fig. 2.12: Simulated subthreshold characteristics of the unit cell                           |   |

| Fig. 2.13: Output characteristics of the unit cell                                           |   |

| Fig. 2.14: Schematic of test circuit used in extracting charge transfer characteristics      |   |

| using CA-AAM                                                                                 |   |

| Fig. 2.15: Simulated charge transfer characteristics of the 0.8 $\mu$ m switch               |   |

| (W=31,878µm)                                                                                 |   |

| Fig. 2.16: Stacked contacts and borderless contacts (a) no stacking and borders (b) stacking | ç |

| and borders (c) stacking and borderless                                                      |   |

.

| Fig. 3.1: Cross section of an LDDMOSFET including pocket implant                         | 42                 |

|------------------------------------------------------------------------------------------|--------------------|

| Fig. 3.2: Steps for pocket implant fabrication (a) LDD and S/D implantation (b) salicies | de                 |

| formation (c) SWS removal and LAT ion-implantation                                       | 43                 |

| Fig. 3.3: Unit cell (a) layout (b) cross section                                         | 44                 |

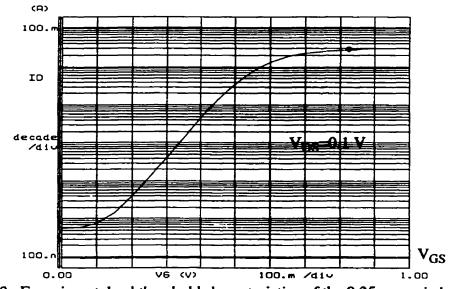

| Fig. 3.4: Transfer characteristics of the unit cell (L <sub>eff</sub> = 0.22 µm)         | 45                 |

| Fig. 3.5: Simulated subthreshold transfer characteristics of the unit cell               | 46                 |

| Fig. 3.6: Output characteristics of the unit cell                                        | 46                 |

| Fig. 3.7: Checkerboard layout pattern for the 0.25 µm switch                             | 47                 |

| Fig. 3.8: Charge transfer characteristics of the 0.25 µm switch W=12,499                 | 48                 |

| Fig. 3.9: Layout of the test chip                                                        | 50                 |

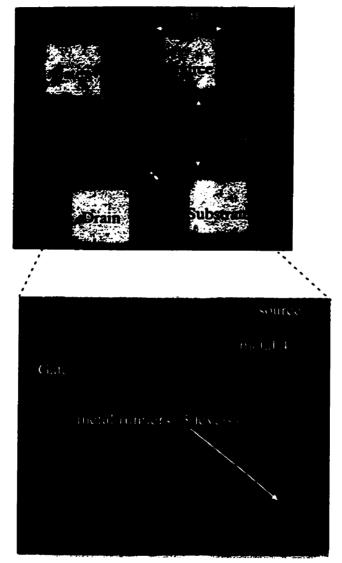

| Fig. 3.10: Micrograph of the 0.25 µm switch                                              | 51                 |

| Fig. 3.11: Experimental output characteristics of the 0.25 µm switch                     | 52                 |

| Fig. 3.12: Experimental transfer characteristics of the 0.25 µm switch                   | 53                 |

| Fig. 3.13: Experimental subthreshold characteristics of the 0.25 µm switch               | 53                 |

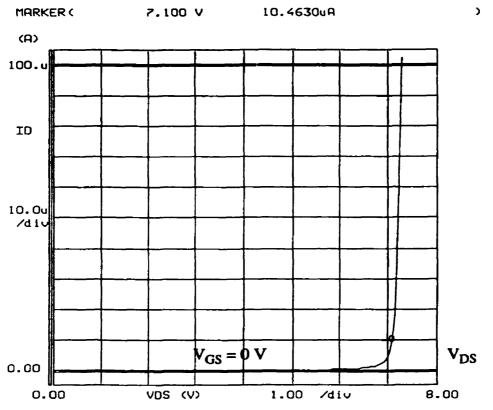

| Fig. 3.14: Breakdown voltage measurements for the 0.25 µm switch                         | 54                 |

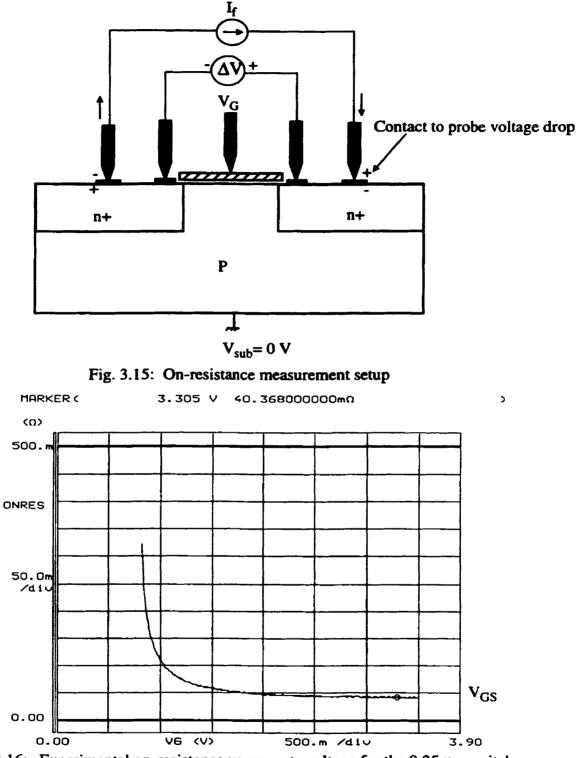

| Fig. 3.15: On-resistance measurement setup                                               | 56                 |

| Fig. 3.16: Experimental on-resistance versus gate voltage for the 0.25 $\mu$ m switch    | 56                 |

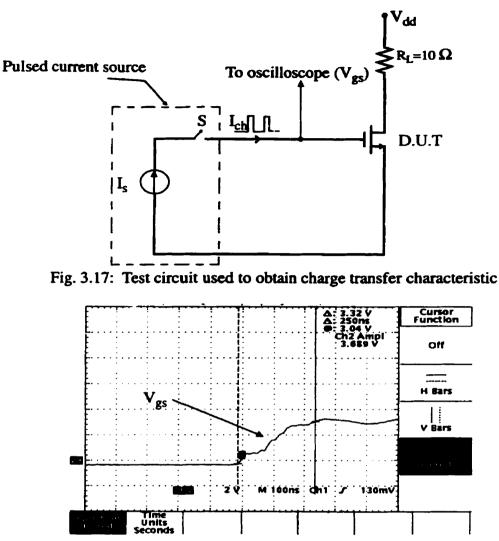

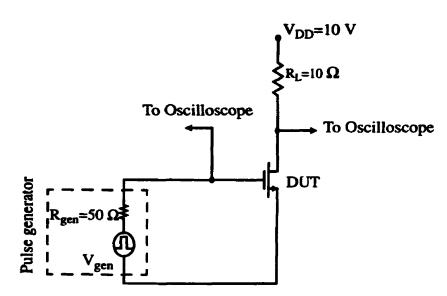

| Fig. 3.17: Test circuit used to obtain charge transfer characteristic                    | 58                 |

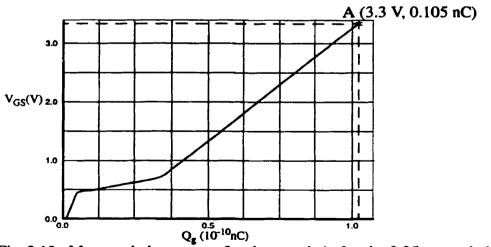

| Fig. 3.18: Gate to source voltage waveforms during the charging of the input capacitanc  | e C <sub>iss</sub> |

| (current pulse 0.42 mA peak)                                                             | 58                 |

| Fig. 3.19: Measured charge transfer characteristic for the 0.25 $\mu$ m switch           | 58                 |

| Fig. 3.20: Test circuit for rise and fall times measurements                             | 59                 |

# CHAPTER 1

## Introduction

In low voltage portable applications, the increase in chip densities and frequency of operation is resulting in higher power requirements. These requirements have a significant impact on system performance associated with reduced battery life-time and have created demand for high efficiency switch mode DC/DC converters to power these systems. These converter modules must also satisfy stringent requirements for compact size and light weight.

To reduce the size and weight of the modules, the size of the reactive components which account for a significant volume of the converter must be reduced. This can be done by increasing the switching frequency[1], however, the price is increased power losses in the semiconductor power switch. In order to enable operation at high switching frequency, the converter efficiency and particularly the power switch efficiency must be improved.

Power converters are presently operating at 300-1000 KHz switching frequencies and are implemented using discrete vertical power MOSFETs, a gate driver IC controller and a low pass filter assembled as an integral part of board-mounted systems. Reported efficiencies range between 92% at 300 KHz to 86% at 1000 KHz. The drop in efficiency at high frequencies is related to losses in vertical power MOSFETs attributed to the inherent high on-resistance and large Miller feedback capacitance associated with the vertical structure. This imposes serious limitations on higher frequency switching operation.

Future converters are expected to be implemented on-chip with projected switching frequencies above 10 MHz and require a new generation of high speed, high efficiency, low

voltage lateral power MOSFETs that can be implemented using VLSI compatible processes.

On-chip monolithic implementation of a switch mode DC/DC converter is quite attractive because of its favorable impact on system reliability, performance and cost due to reduced parts count, area savings and elimination of external interconnects.

The reason for choosing MOSFET's rather than bipolar transistors for the implementation of the converter switch is due to the inherent advantages of the former in low voltage switching applications [2,3,4]. These include: 1) high input impedance that considerably simplifies the gate drive circuitry and improves the efficiency, and 2) fast switching speed associated with the lack of the minority carrier storage effects and 3) negative temperature coefficient of current, hence, no thermal runaway.

#### 1.1 Power Losses in Switch Mode DC/DC Converters

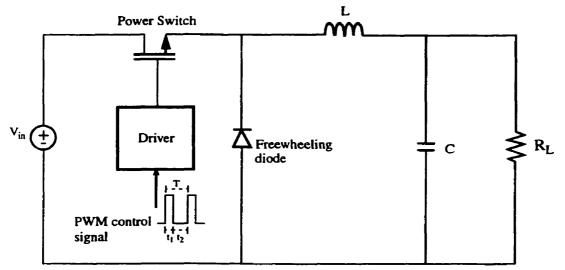

Most portable systems utilize switch mode DC/DC converters known as step-down (buck) converters to convert a higher input voltage into a lower output voltage. The main building blocks of the buck converter are illustrated in Fig. 1.1.

Fig. 1.1: Switch mode DC/DC converter

The gate of the power switch is driven by a pulse width modulated (PWM) control signal, that results in one of three possible states of operation for the switch:

i) The off-state: The gate voltage is low and the power switch is turned off. The device should be able to support a voltage larger than the supply voltage. This voltage is termed the forward blocking capability of the switch. The power losses due to the leakage current in the off-state are relatively small and can be assumed zero.

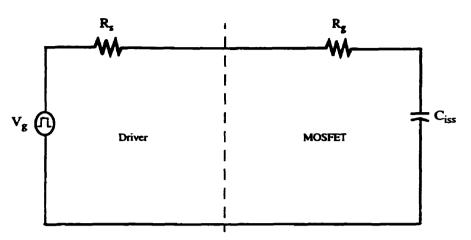

ii) The switching state: The switch is in a transition period and switches form one state to the other as dictated by the gate driver voltage. An ideal switch exhibits an instantaneous transition (zero turn on and turn off times), however, a real switch exhibits finite switching time due to the charging and discharging of the input capacitance associated with the gate of the MOSFET structure, this in turn results in dynamic power dissipation known as the switching loss. The input capacitance  $C_{iss}$  is voltage dependent and is equal to  $C_{gs} + (1+A_v)$  $C_{gd}$  where  $C_{gs}$  is the gate to source capacitance, the term  $(1+A_v)C_{gd}$  accounts for feedback capacitance and  $A_v$  is the forward voltage gain in the common source configuration. Another source of power dissipation occurring during the switching mode of operation is the gate drive loss and is associated with the gate resistance  $R_g$  as shown in Fig. 1.2[5]. This resistance is arising from the gate electrode internal to the device[6] and is responsible for power dissipation during the charging or discharging of the input capacitance  $C_{iss}$ .

iii) The on-state: The gate voltage is high and the power switch is conducting in the triode region. During the on-state the switch behaves as a finite resistor defined by the device on-resistance, that is, the total resistance between the source and the drain contacts. The current passing through the switch is the on-current  $I_{on}$  and the voltage across it is the  $V_{ds-on}$ . Ideally the on-resistance and therefore  $V_{ds-on}$  should be zero, however, a real switch has a non-zero on-resistance and therefore dissipates a finite amount of power (conduction losses)

CMOS Compatible Power MOSFETs for On-Chip DC/DC Converters University of Toronto

Fig. 1.2: Gate drive equivalent circuit

The total power dissipation  $P_d$  in a MOSFET switch can be expressed as

$$P_{d} = f_{s} \left( I_{on}^{2} R_{on} t_{1} + t_{on} \int_{0}^{t} v_{on}(t) i(t) dt + t_{off} \int_{0}^{t} v_{on}(t) i(t) dt + \frac{R_{g}}{R_{g} + R_{s}} V_{gs} Q_{g} \right)$$

(1.1)

where  $f_s$  is the switching frequency of the MOSFET,  $I_{on}$  is the switch current during conduction,  $R_{on}$  is the switch on-resistance,  $t_1$  is the switch conduction time,  $t_{on}$ ,  $t_{off}$  are on and off switching time,  $R_g$  is the gate resistance of the switch,  $R_s$  is the driver circuit output resistance,  $V_{gs}$  is the peak voltage at the gate and  $Q_g$  is the peak gate charge that is required to completely switch the device.

The first term in equation (1.1) represents the conduction losses in the switch and is proportional to the device on-resistance which in turn is dependent on the device structure, doping profile, gate voltage and temperature. The second and third terms represent the switching losses which are proportional to the switch turn-on and turn-off times and hence depend on the input capacitance of the MOSFET. The last term represents the gate drive loss dissipated internally in the MOSFET gate resistance and is proportional to the total gate charge  $Q_g$ . From the above discussion, it can be seen that the total losses are directly proportional to the switching frequency implying that while the increase of operating frequency is desirable to reduce the size of capacitance C and inductance L in the converter circuit of Figure 1.1, it has a negative impact on the total power losses in the semiconductor switch. This represents the most important trade-off in designing switch mode converters.

#### 1.2 Current status of Power MOSFET switches

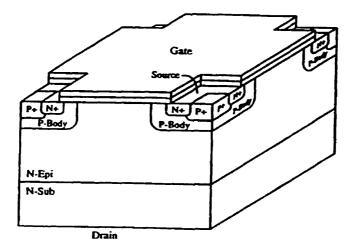

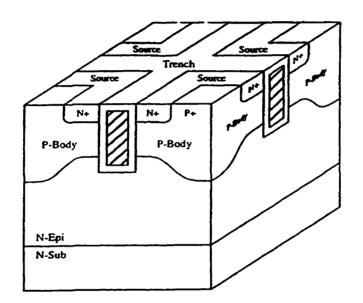

Traditionally, MOSFET switches in DC/DC converters are implemented in either Planar Vertical Double Diffused MOSFETS (VDMOST) or Trench MOSFETS (TMOST) [8],[9]. In the VDMOST, shown in Fig. 1.3, current emanating from the source flows laterally along the surface, then vertically between adjacent P-body diffusions, through the epitaxial drain and substrate and out the wafer's backside. This long path of current flow translates into a large on-resistance. In other words, VDMOST devices suffer from inherent high on-resistance due to substrate, epi-layer and parasitic JFET pinch resistance (between the two adjacent body region)[8]. Reduction of the on-resistance can be achieved by increasing the packing cell densities through scaling down of the surface geometry.

Fig. 1.3: Vertical DMOST cross section

To solve the problem associated with the parasitic JFET effects in VDMOS devices, the TMOST shown in Fig. 1.4, was proposed [10]. The current flow is still vertical along the sidewall of the trench. While the TMOST solves the JFET problem, reduction in the on-resistance is still limited by the substrate and epi-layer resistances.

Finally, the incompatibility of vertical power MOSFETs with standard CMOS or BiCMOS processes makes them unsuitable for monolithic implementation of high frequency switching mode DC/DC converters.

Fig. 1.4: TMOST cross section

#### **1.3 Lateral Power MOSFETs**

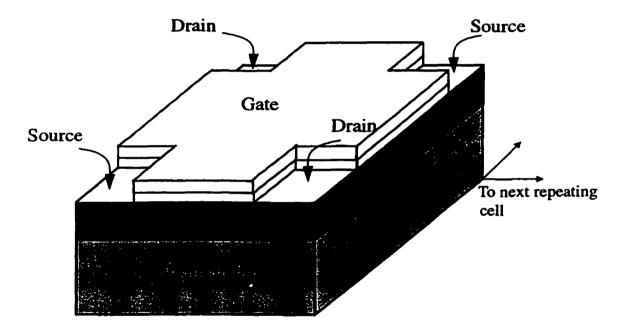

In low voltage converter applications, high breakdown voltage is not a requirement since the switch needs to support a low voltage (less than 5 V) when it is in the off-state. This fact makes the implementation of lateral Power MOSFETs in a VLSI technology very attractive. The advantages of lateral power MOSFETs, shown in Fig. 1.5, are:

- ii) low total gate charge  $Q_g$ , gate to source and gate to drain capacitances, and

- iii) low on-resistance associated with high packing density and lateral current flow<sup>1</sup>.

Lateral devices implemented using a VLSI process can take advantage of aggressive design rules which in turn reduce the cell pitch, increase the cell packing density resulting in low specific on-resistance  $R_{on^*}$  A. The on-resistance also determines the device area for a given current handling capability requirement in the on-state. Since the input capacitances  $C_{gs}$  and  $C_{gd}$  are proportional to the total area of the device, aggressive VLSI technologies result in low input capacitances and total gate charge  $Q_g$ .

Fig. 1.5: Lateral MOSFET cross section(unit cell)

#### 1. resistance contributions due to substrate and JFET pinching effect are eliminated.

### 1.4 Figure Of Merit for Power Switches

To compare the performance of different power devices, a Figure of Merit (FOM)[11] is commonly used by power MOSFETs manufacturers and is defined as

$$FOM = R_{on} \times Q_g \tag{1.2}$$

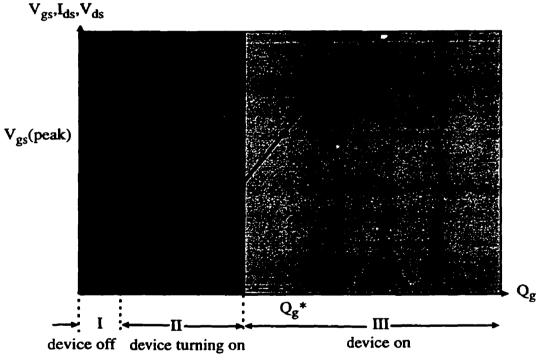

where  $R_{on}$  is the device on-resistance and  $Q_g$  is the total gate charge when the device is completely switched on. The value of  $Q_g$  can be extracted from the charge transfer characteristics, shown in Fig. 1.6, which is a plot of the gate to source voltage  $V_{gs}$  versus the gate charge  $Q_g$ . This curve can be obtained using the test circuit shown in Fig. 1.7.

Fig. 1.6: Charge transfer characteristics

There are three distinct regions of importance in this plot. In region I, the device is off, the gate voltage  $V_{gs}$  is determined by the voltage across the input capacitance  $C_{iss}=C_{gs}+C_{gd}$ . The voltage increases linearly in this region until the device starts to turn on.

In region II, the gate voltage turns on the device, the drain current increases, the drain voltage drops and the gate voltage increases slowly as a function of input charge as long as  $V_{ds}$  is dropping and  $I_{ds}$  is increasing. The input capacitance  $C_{iss}$  is now given by the equation

$$C_{iss} = C_{gs} + (1 + |A_v|)C_{gd}$$

(1.3)

In region III,  $V_{ds}$  reaches  $V_{ds-on}$  and the current settles to its final value. The input capacitance  $C_{iss}$  is approximately  $C_{gs} + C_{gd}$ . The input gate charge  $Q_g^*$  (at point A) corresponding to  $V_{gs}$ (peak) can be determined from that graph.

Fig. 1.7: Test circuit for charge transfer characteristics

### 1.5 Thesis Objective and Organization

Previous publications[11,12] have dealt with the design of high load current (8-13A) power switches for the implementation of voltage regulator modules (VRM) intended for microprocessor applications. It was shown that the lower the FOM the higher the efficiency of the converter[11]. Extrapolation of the reported results suggests that a converter efficiency of 95% can be achieved using a device with FOM less than 10 m $\Omega$ nC. To the best of our knowledge, there are no published reports that deal with the implementation of CMOS compatible power switches for the 1 A current range category and the majority of state of the art converters are still being implemented using discrete components.

This thesis deals with the design and implementation of a 1 A - low voltage power MOSFET switch using submicron CMOS compatible processes, the target application is high efficiency on-chip switch mode DC/DC converters for portable applications that utilizes dynamic voltage scaling (voltage scheduler algorithms) such as Personal Digital Assistants (PDA's) and digital cameras where load currents are in the range of 0.5 to 1A.

The major specifications of the switch are

- Threshold voltage < 0.6 V

- Breakdown voltage  $\geq 5 \text{ V}$

- Current carrying capability  $\geq 1$  A

- Figure of Merit (FOM) requirement:  $R_{on} \times Q_g < 10 \text{ m}\Omega \text{nC}$

- Switching frequency  $\geq$  10 MHz.

In this thesis two devices are investigated. In Chapter 2 processing steps, technology issues and optimization of a 0.8  $\mu$ m single level metallization, N-channel MOSFET are discussed. The design uses 0.8  $\mu$ m base line and single level metallization which are achievable at the Microelectronics Research Laboratory (MRL). In Chapter 3 the design, implementation and characterization of an optimized switch using a commercial 0.25  $\mu$ m - 5 level metallization CMOS process are presented. Finally, conclusions along with suggestions for future work are presented in Chapter 4.

### References

- [1] C. R. Sullivan, "Microfabrication of Magnetic Components for High Frequency Power Conversion", Ph.D. Dissertation, University of California at Berkeley, 1996.

- [2] K. Shenai, "Accurate Characterization of Gate Resistance and High-Frequency Switching Efficiency of a Power MOSFET", Power Electronics Specialists Conference (PESC), Proceedings, pp. 107-112, 1990.

- [3] N. Fujishima, "A Novel Trench Lateral Power MOSFET with High Breakdown Voltage and Low On-Resistance", M.A.Sc. Thesis, University of Toronto, 1998.

- [4] C. A. T. Salama, "Process Technology Options" Course Notes, High Voltage and Power IC Design, ISPSD, Short Course, 1999.

- [5] Siliconix Incorporated, "MOSPOWER Applications Handbook", Santa Clara, California, 1984.

- [6] B. J. Baliga, "Power Semiconductor Devices" PWS Publishing Company, Boston, 1996.

- [7] B. Murari, F. Bertotti, G. A. Vignola, "Smart Power ICs, Technologies and Applications", Springer, New York, 1996.

- [8] R. K. Williams, K. Owyang, H. Yilmaz and W. Grabowski, "Complementary Trench MOSFETs Define New Levels of Performance" TEMIC Semiconductors publications.

- [9] P. Rossel, H. Tranduc and G. Charitat, "Power MOS Devices: Structures and Modeling", International Conference on Microelectronics, Proceedings, pp. 341-352, 1995.

- [10] D. Ueda, H. Takagi and G. Kano, "An Ultra-Low On-Resistance Power MOSFET Fabricated by Using a Fully Self-Aligned Process", IEEE Transactions on Electron Devices, vol. ED-34, pp. 926-930, 1987.

- [11] A. Q. Huang, N. Sun, B. Zhang, Z. Zhou and F.C. Lee "Low Voltage Power Devices for Future VRM" International Symposium on Power Semiconductor Devices & ICs (ISPSD), Proceedings, pp. 395-398, 1998.

- [12] N. X. Sun, A. Q. Huang and F.C. Lee "0.35 μm, 43 μΩcm2, 6 mΩ Power MOSFET to Power Future Microprocessor" International Symposium on Power Semiconductor Devices & ICs (ISPSD), Proceedings, pp. 77-80, 1999.

# **CHAPTER 2**

# 1-A Power MOSFET in 0.8 µm CMOS Technology

#### 2.1 Introduction

In this chapter, an N-channel power MOSFET switch capable of carrying 1 A of current in the on-state is presented. The device is based on a low-voltage lateral CMOS technology with minimum line width of 0.8  $\mu$ m and a single level metallization dictated by the processing capabilities in the Microelectronics Research Laboratory at the University of Toronto.

Two-dimensional process simulations were performed using TSUPREM-4 to optimize the device structure and doping profiles. This was followed by two-dimensional device simulations using MEDICI. MEDICI's Circuit Analysis Advanced Application Module (CA-AAM) was used to obtain the charge transfer characteristics of the power switch from which the total gate charge value  $Q_g$  was extracted.

#### 2.2 1-A Power Switch in 0.8 µm CMOS Process

On-chip implementation of switch mode DC/DC converter implies that the power MOSFET switch, the reactive components and the control circuits must all be implemented on the same silicon chip. The implementation process must be fully CMOS compatible. Furthermore, the power switch must meet the specifications and performance requirements for high-efficiency switch mode converters, particularly a low  $R_{on} \times Q_g$ .

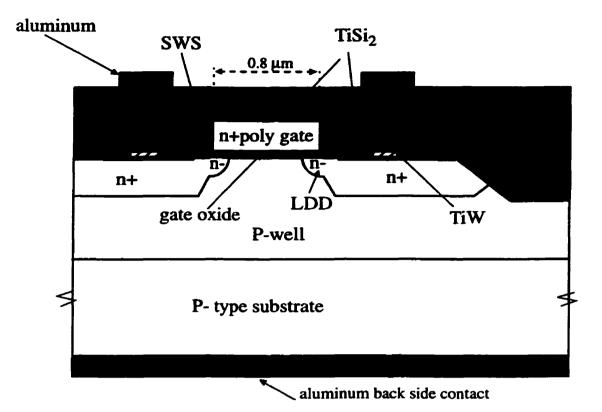

A cross section of the proposed 0.8  $\mu$ m N-channel MOSFET unit cell is shown in Fig. 2.1. The 0.8  $\mu$ m feature size mentioned above defines the minimum drawn gate length. The low doped drain region LDD is required in small channel devices because it enhances

Page 13

the device immunity to: (1) hot carrier injection which can limit the lifetime of MOSFET devices and (2) parasitic bipolar action.

The process incorporates self-aligned silicide (salicide process) using titanium to reduce the source/drain contact resistance contribution to the switch on-resistance and to enhance the switching speed. The salicide process is very attractive because no extra mask is needed. The gate side wall spacer oxide (SWS) is formed by anisotoropic reactive ion etching (RIE) which: (1) allows the formation of low doped drain junction (LDD) by selectively masking the subsequent heavy arsenic ion-implantation (n+ implant) and (2) prevents bridging between the gate and the source/drain electrodes during the salicide process.

The process features a thin gate oxide (100 Å) to boost current drive and alleviate short channel effects. The lower limit of the oxide thickness is set by fabrication reproducibility. Shallow source/drain junctions are used in the process to minimize short channel effects. The process specifications of the 0.8  $\mu$ m MOSFET unit cell illustrated in Fig. 2.1 are summarized in Table 2.1.

| Parameter/Units                                  | Symbol                | Value              |

|--------------------------------------------------|-----------------------|--------------------|

| Threshold Voltage (V)                            | V <sub>th</sub>       | 0.32               |

| Subthreshold Swing (mV/decade)                   | S                     | 80.34              |

| Gate Oxide Thickness (Å)                         | t <sub>ox</sub>       | 100                |

| P-well Depth (µm)                                | X <sub>j-p-well</sub> | 1.5                |

| P-well Surface Concentration (cm <sup>-3</sup> ) | N <sub>p-well</sub>   | 8×10 <sup>16</sup> |

| Poly Gate Thickness (µm)                         | t <sub>poly</sub>     | 0.45               |

| Polycide Sheet Resistance (Ω/□)                  | R <sub>poly</sub>     | <10                |

| Source/Drain Junction Depth (µm)                 | Xj                    | 0.22               |

| S/D Sheet Resistance (Ω/□)                       | R <sub>sd</sub>       | <10                |

| S/D Breakdown Voltage (V)                        | BV <sub>DS</sub>      | 9                  |

Table 2.1: Process specifications of the 0.8 µm unit cell

CMOS Compatible Power MOSFETs for On-Chip DC/DC Converters Univ

Fig. 2.1: Cross section of the 0.8 µm N-channel lateral MOSFET

#### 2.3 Design Criteria for Low-Voltage Power Switch

#### 2.3.1 Specific On-Resistance

The power losses in the switch during conduction is proportional to the on-resistance. The on-resistance is determined by the total resistance between the source and drain contacts. Although the on-resistance can be reduced by paralleling many individual unit cells using specific layout techniques such as interdigitated or checkerboard patterns, chip area and junction capacitances accordingly increase. Therefore, specific on-resistance  $R_{on-sp}$ , which is the product of the on-resistance and the device area, is more commonly used as a measure of performance to compare different switches.

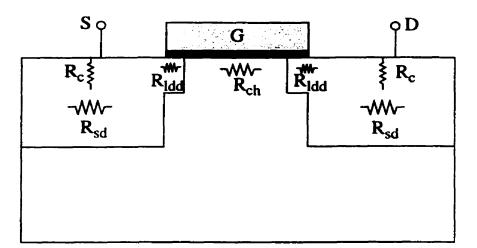

For a LDD N-channel MOSFET, the total specific on-resistance consists of four components, as illustrated in Fig. 2.2 and is given by

$$R_{on-sp} = R_{ch-sp} + 2R_{ldd-sp} + 2R_{sd-sp} + 2R_c$$

(2-1)

where  $R_{ch-sp}$  is the specific resistance of the channel,  $R_{ldd-sp}$  is specific resistance of the LDD regions,  $R_{sd-sp}$  is the specific resistance of the S/D junctions and  $R_c$  is the S/D specific contact resistance.

The specific channel resistance can be expressed as

$$R_{ch-sp} = WL \frac{L}{W\mu_{ns}C_{ox}(V_{GS} - V_{th})} = \frac{L^2}{\mu_{ns}C_{ox}(V_{GS} - V_{th})}$$

(2-2)

where W is the channel width, L is the channel length,  $\mu_{ns}$  is the mobility of electrons in the channel,  $V_{th}$  is the threshold voltage,  $V_{GS}$  is the gate voltage and  $C_{ox}$  is the gate oxide capacitance per unit area and is given by

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}}$$

(2-3)

where  $\varepsilon_{ox}$  is the oxide permittivity and  $t_{ox}$  is the gate oxide thickness.

The channel specific resistance is the largest among the resistive components and as indicated in Equation 2-2 is dependent on the channel mobility, the channel length, threshold voltage and oxide thickness  $t_{ox}$ . The specific resistance  $R_{ldd-sp}$  is associated with the LDD regions and is given by

$$R_{ldd-sp} = WL_{ldd} \frac{L_{ldd}}{W\mu_{na}C_{ox}(V_{GS}-V_{th-ldd})} = \frac{L_{ldd}^{2}}{\mu_{na}C_{ox}(V_{GS}-V_{th-ldd})}$$

(2-4)

where  $L_{Idd}$  is the effective length of the LDD region,  $\mu_{na}$  and  $V_{th-Idd}$  are the electron mobility and the threshold voltage in the LDD region, respectively. The specific source/drain resistance  $R_{sd-sp}$  is due to the n+ junctions and is dependent on the junction depth and the doping concentration. The last term in Equation(2-1) is the specific contact resistance which is directly proportional to the contact resistivity. A reduction in the contact specific resistance can be achieved by using self-aligned selicide in the source/drain junctions.

Fig. 2.2: Cross section of the LDD MOSFET structure indicating different components of the on-resistance

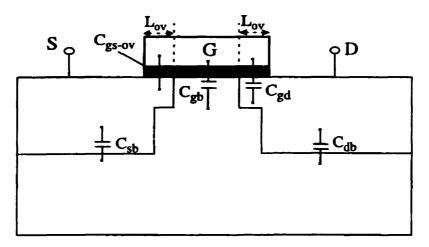

#### 2.3.2 Input Capacitance C<sub>iss</sub>

As discussed in Chapter 1, the switching plus gate drive losses are proportional to the switching times  $t_r$ ,  $t_f$  and the total gate charge  $Q_g$ . The switching time is proportional to the carrier transit time across the channel and the rate of charging and discharging of the input capacitance  $C_{iss}$  associated with the gate of the MOSFET structure. The carrier transit time is inversely proportional to the channel length L. Thus, a short channel length is preferable for high speed. The different capacitive components associated with the MOSFET structure are illustrated in Fig. 2.3. The input gate capacitance  $C_{iss}$  has two components,  $C_{gs}$  and  $C_{gd}$  (Miller feedback capacitance). The gate to source capacitance  $C_{gs}$  is due to overlap capacitance between the gate electrode and the source junction  $C_{gs-ov}$  and the gate to bulk capacitance  $C_{ox}$  and the space-charge capacitance. The maximum value of  $C_{gb}$  is equal to  $C_{ox}$  which occurs under accumulation conditions. The gate to drain capacitance is

determined by the overlap length between the gate electrode and drain junctions  $L_{ov}$  and the gate oxide thickness.

Fig. 2.3: Cross section of the LDD MOSFET indicating various capacitance components in the structure

For accurate estimation of the input capacitance, the fringing capacitances may also be added to  $C_{gs}$  and  $C_{gd}$ .

Due to the "distributed RC network" nature of the channel of MOSFETs and their voltage dependence, the exact modeling of the MOSFET during switching is not a straightforward practice[1], however, by examining the device parameters contributing to  $C_{iss}$ , a design criteria for minimizing the input capacitance can be established. The design criteria are: small gate to source and gate to drain overlap lengths, reduced channel area (W.L), hence, the requirement for shorter channel length and higher current drive.

#### 2.3.3 Short Channel Effects

Scaling of MOSFETs is not free from performance and reliability degradations. Issues such as threshold voltage roll-off (which sets the lower limit for MOSFET physical gate length)[2], hot carrier injection and parasitic BJT action are known to be the most serious problems associated with short channel devices. For no short channel effects the minimum channel length of a MOSFET for a certain technology can be calculated using the following empirical relationship[3]

$$L_{\min} = 0.4[r_{j}t_{ox}(W_{S} + W_{D})^{2}]^{1/3}$$

(2-5)

where  $r_j$  is the junction depth in  $\mu m$ ,  $t_{ox}$  is the oxide thickness in Å and  $W_S$  and  $W_D$  are the depletion region widths in  $\mu m$  at the source and drain junctions, respectively. Generally, as long as the channel length is larger than  $L_{min}$  the device maintains long channel behaviour. It can be concluded, from Equation 2-5, that to promote long channel behaviour, the junction depth and oxide thickness must be reduced and the background concentration must be increased.

#### 2.3.4 Subthreshold Current

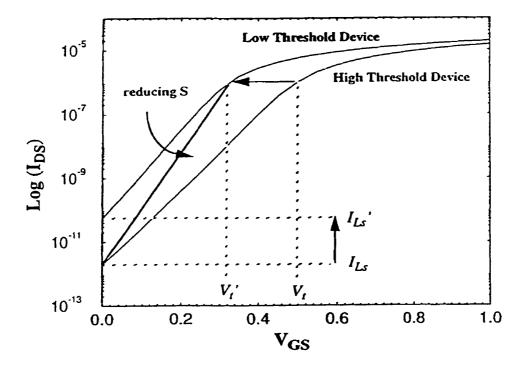

The fundamental theory of the MOSFET assumes that no drain current exists when the gate to source voltage is lower than the device threshold voltage. In real devices, however, there is a weak current conduction known as the subthreshold leakage current. In battery-powered portable applications, this leakage current can significantly reduce the battery lifetime. The lower the threshold voltage the higher the off-state current (at  $V_{GS}=0$ ) as demonstrated in Fig. 2.4 ( $I_{LS} < I_{LS}'$ ).

The subthreshold current is related to the threshold voltage through the equation

$$I_{Ls} = I_o \frac{W}{L} e^{\frac{qn(V_{GS} - V_{th})}{KT}} \left(1 - e^{\frac{-qV_{DS}}{KT}}\right)$$

(2-6)

where I<sub>o</sub> is the characteristic current and n is given by

$$n = \left(1 + \frac{C_{dep}}{C_{ox}}\right)^{-1}$$

(2-7)

in which  $C_{ox}$  and  $C_{dep}$  are the oxide and depletion capacitances per unit area, respectively

#### The off-state leakage current can be obtained from the equation

$$I_{off} = A.10^{\frac{-V_{th}}{S}}$$

(2-8)

It can be seen, form Equation 2-8, that a low  $I_{off}$  requires higher threshold voltage and lower subthreshold swing S. To reduce S, the channel doping and oxide thickness must be lowered.

The subthreshold swing S is used to characterize the subthreshold behavior of MOSFETs and is defined as the inverse of the rate of a decade decrease in current with  $V_{GS}$  reduction and is given by

$$S = \frac{\partial V_{GS}}{\partial \log I_{SL}} = 2.3 \frac{KT}{q} \left( 1 + \frac{C_{dep}}{C_{ox}} \right)$$

(2-9)

It is desirable to have a low value of S. The lower theoretical limit of S is equal to 59.8 mV/decade (2.3 KT/q) at  $T=300^{\circ}$ K.

Fig. 2.4: Effect of V<sub>t</sub> scaling on subthreshold leakage current[4]

#### 2.3.5 Hot Carrier Injection & Parasitic Bipolar Action

Another important phenomenon associated with short channel MOSFETs is the hot carrier injection (HCI). This phenomenon occurs when channel carriers entering the high electric field region near the drain end of the channel gain sufficient energy to overcome the  $Si-SiO_2$  surface barrier and are injected into the oxide. These carriers can cause damage to the  $Si-SiO_2$  interface and result in trapped charge in the oxide. As a consequence, shifts in the transistor threshold voltage, transconductance and drain saturation current can take place.

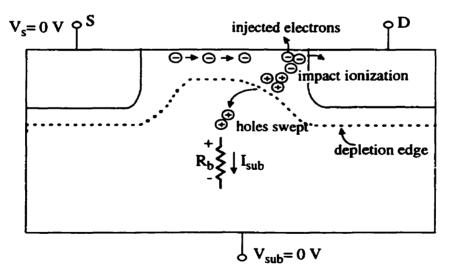

Associated with HCI is another mechanism known as parasitic bipolar action illustrated in Fig. 2.5. When the electric field near the drain end of the channel exceeds 100 KV/cm, channel carriers gain enough energy, to cause impact ionization resulting in electron-hole (e-h) pair generation[5]. The electrons drift to the drain while holes are swept to the bulk, creating a substrate current  $I_{sub}$  which gives rise to a potential difference between the substrate back contact and the bulk. This voltage drop results in forward biasing of the source to bulk diode which in turn results in more carrier injection in the channel.

Fig. 2.5: Parasitic bipolar action in short channel MOSFETs

The injected channel carriers are accelerated towards the drain causing more e-h pair generations via impact ionization through regenerative feedback resulting in an increase in the drain current which if excessive can result in device failure. The mechanism resembles the operation of a bipolar transistor where the source acts as the emitter, the substrate as the base and the drain as the collector.

To alleviate HCI effects and parasitic BJT action, low doped drain junctions are inserted between the heavily doped drain and the channel. These LDD regions relax the lateral electric field distribution and spread it laterally, thus, lowering the maximum electric field[6-7]. The penalty in using LDD regions is the increase in the on-resistance, however, this penalty is imposed by the necessity to design a reliable device that can perform well over time.

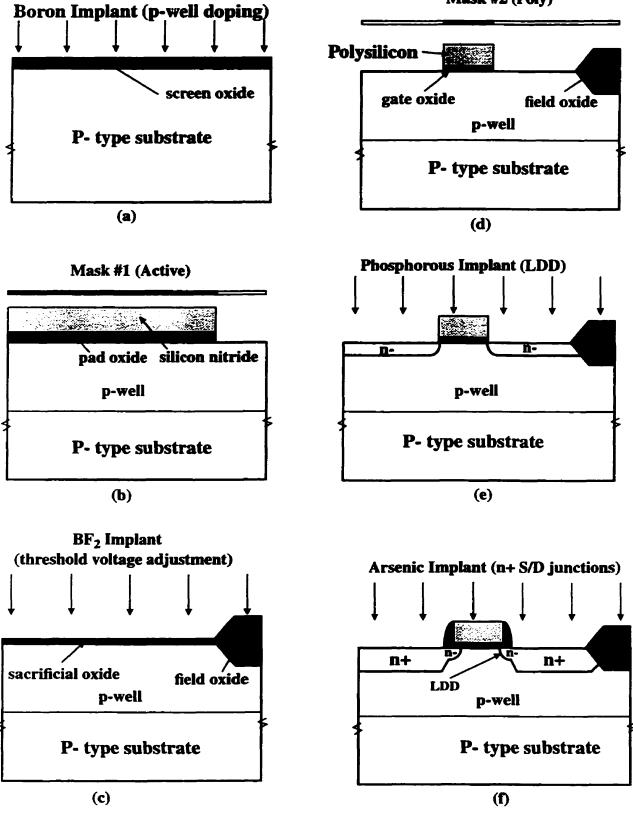

#### 2.4 Process Description

The process involved in the fabrication of the unit cell is described with reference to Fig. 2.6. Starting with a 18-20  $\Omega$ -cm, p-type wafers with <100> orientation, a p-well implant is carried out through a thermally grown 300Å screen oxide as shown in Fig. 2.6(a). The dopant impurities are then driven-in at 1000 °C for 150 minutes in nitrogen ambient.

Low pressure chemical vapor deposition (LPCVD) of silicon nitride film (1200Å) is performed and photolithography using mask #1 (active) is used to define the active regions as shown in Fig. 2.6(b). Local oxide (LOCOS) is grown at 950°C for approximately four hours in wet  $O_2$  resulting in 7000Å of oxide everywhere except for the area protected by the silicon nitride (active region).

The nitride and the pad oxide are removed and a thin layer of sacrificial oxide (400Å) is thermally grown at 950°C to remove any silicon nitride (white ribbon) formed on the silicon surface due to the chemical reaction between  $NH_3$  and the silicon surface during the lengthy LOCOS growth.

Page 22

A threshold voltage adjustment implant using  $BF_2$  with a dose of  $8 \times 10^{13}$  cm<sup>-2</sup> and energy of 25 keV is performed to raise the channel surface concentration, as shown in Fig. 2.6(c).  $BF_2$  has low projected range making it more suitable for this specific process, compared to boron. The sacrificial oxide is then etched and the gate oxide is grown in dry oxygen (1100 °C, 6.5 minutes). The process incorporates 2% HCl to eliminate mobile charges (mainly positive alkali metal ions) in the gate oxide. The process is followed by a 30 minutes anneal in a N<sub>2</sub> ambient to reduce the fixed oxide charge and the interface trapped charge.

In-situ doped polysilicon with a thickness of 4500Å is then deposited by LPCVD. Wet etching of the polysilicon and the underlying oxide from the back side of the wafer is performed. The polysilicon is defined using mask #2 (poly) and etched by reactive ion etching (RIE) using clorine as shown in Fig. 2.6(d).

During RIE etching of the gate, some damage occurs to the gate oxide underneath the polysilicon and to the substrate[8]. Therefore, it is necessary to follow the RIE process by rapid thermal annealing (RTA) at 900°C for 1.5 minutes in an oxygen ambient. Thereafter, the LDD implant is performed using phosphorous  $(2.5 \times 10^{13} \text{ cm}^{-2}, 40 \text{ keV})$ , as shown in Fig. 2.6(e). Next, fabrication of the side wall spacer (SWS) is carried out a 4500Å LPCVD oxide followed by oxide densification at 900°C for 40 minutes in a N<sub>2</sub> ambient<sup>1</sup> and finally directional RIE etching of the oxides is performed to define the side wall spacer.

The source/drain junctions are fabricated, by arsenic ion-implantation with a dose of  $4.7 \times 10^{15}$  cm<sup>-2</sup> and energy of 70 keV through a 200Å deposited oxide. The implantation is self-aligned to the edge of the SWS rather than to the polysilicon causing the highly doped n+ junction to be positioned away from the channel end as shown in Fig. 2.6(f).

University of Toronto

<sup>1.</sup> This annealing process drives-in phosphorous impurities under the gate.

Mask #2 (Poly)

Fig. 2.6: 0.8 µm N-channel process flow

Thereafter, an 800Å oxide film is deposited using LPCVD and arsenic activation is carried out by RTA for 40 seconds at 1050 °C in  $N_2$  ambient. The purpose of the oxide deposition is to prevent auto-doping during the RTA process.

Self-aligned titanium silicide (salicide) steps are carried out [9-10]. First the oxide is wet- etched from the top of the gate, source and drain areas. A thin film of titanium (50 nm) is blanket-sputtered on the surface, followed by a short RTA process (650 °C, 1 minute) in  $N_2$  ambient. It is necessary to control carefully the temperature and time during this process to prevent lateral bridging between the gate electrode and the S/D junctions. The nitrogen helps to limit "silicon pumping" and to confine the chemical reaction to regions where titanium and silicon are effectively in physical contact.

Next, selective wet etching of the unreacted titanium is performed using  $H_2O_2$ : NH<sub>4</sub>OH. The result at this stage is the high-resistance metastable phase of TiSi<sub>2</sub>. Transformation to the low-resistance phase is done by a second RTA step at 850°C for 30 seconds. The cross-section of the structure after Salicide formation is shown in Fig. 2.6(g). A 3000 Å oxide layer is deposited, and the oxide is densified by RTA at 800°C for 2 minutes. Photolithography is performed using mask #3 (contact) to define the contact area and contact opening is carried out using RIE as shown in Fig. 2.6(i).

A blanket layer of titanium tungsten alloy (1000 Å) is sputtered and followed by sputtering of 1  $\mu$ m layer of aluminum. The titanium tungsten is used to prevent aluminum spiking through the junctions.

Photoresist is patterned using mask #4 (metal). Aluminum is wet etched and the photoresist is removed. TiW is then selectively wet etched using  $H_2O_2$  with the aluminum acting as a mask.

Annealing in forming gas is performed for 25 minutes at 450°C to reduce the contact resistance and the interface trapped charge. The cross-section of the device at the end of the process is shown in Fig. 2.6(j). The process flow used in the fabrication of the 0.8  $\mu$ m process is summarized in Table 2.2.

ς.

| Step                                                                            | Process                                                                                                                   |  |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| Starting material                                                               | 4" <100> p-type wafers, resisitivity=18 to 20Ω-cm                                                                         |  |

| Screen gate oxide                                                               | 1000°C, 28 min., dry O2, Thickness=300Å                                                                                   |  |

| P- well implant                                                                 | Ion-implantation, boron, Dose=4x10 <sup>12</sup> cm <sup>-2</sup> ,<br>Energy=20keV.                                      |  |

| Well dopant drive-in                                                            | 1000°C, 150 min., nitrogen ambient                                                                                        |  |

| Screen oxide etch                                                               | Wet etching in 10% buffered HF                                                                                            |  |

| Pad oxide growth                                                                | 1000°C, 28 min., dry O2, Thickness=300Å                                                                                   |  |

| Depositing of silicon nitride                                                   | LPCVD of nitride, thickness=1200Å                                                                                         |  |

| Patterning the nitride                                                          | Photolithography using mask #1, RIE of nitride and wet etching of the oxide                                               |  |

| LOCOS growth                                                                    | 950°C, dry O2, 5 min.<br>950°C, wet O2, 240 min.<br>950°C, dry O2, 5 min.<br>950°C, nitrogen, 20 min.,<br>thickness=7000Å |  |

| Nitride and pad oxide removal                                                   | Oxide wet etching, 1 min.<br>Nitride wet etching, 14:20 min.<br>Oxide wet etching, 45 seconds                             |  |

| Sacrificial oxide growth                                                        | 950°C, dry O2, 80 min., thickness=400Å,<br>oxide wet etching                                                              |  |

| Gate oxide growth                                                               | 1100°C, O2=8%, HCl=2%, N2=90%,<br>6.5 min,<br>thickness=100Å<br>1100°C, N2, 30 min.(annealing)                            |  |

| Deposition of polysilicon gate                                                  | LPCVD of in-situ doped polysilicon, thick-<br>ness=4500Å                                                                  |  |

| Wet etching of the polysilicon and<br>oxide layer from the back of the<br>wafer | PR application on the surface of the wafer,<br>wet etching of the polysilicon and oxide lay-<br>ers from the back         |  |

| Deposition of oxide                                                             | LPCVD of oxide, thickenss=2500Å                                                                                           |  |

| Table 2 | 2.2: 0.8 | μm | process | summary |

|---------|----------|----|---------|---------|

|---------|----------|----|---------|---------|

| Step Process                                                |                                                                                                                                                                   |  |  |  |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Defining the gate structure                                 | Photolithography (mask #2), RIE of oxide,<br>and polysilicon layers                                                                                               |  |  |  |

| RTA annealing                                               | 900°C, 2 min., O2 ambient                                                                                                                                         |  |  |  |

| Formation of LDD S/D junctions                              | Ion-implantation, phosphorous,<br>Dose=2.5x10 <sup>13</sup> cm <sup>-2</sup> , Energy=40keV.                                                                      |  |  |  |

| Deposition of oxide                                         | LPCVD of oxide, thickenss=4500Å                                                                                                                                   |  |  |  |

| Densification of oxide and phospho-<br>rous dopant drive-in | 900°C, 40 min., N2                                                                                                                                                |  |  |  |

| SWS formation                                               | Directional RIE of oxide                                                                                                                                          |  |  |  |

| Deposition of screen oxide                                  | LPCVD of oxide, thickenss=200Å                                                                                                                                    |  |  |  |

| Formation of n+ S/D junction                                | Ion-implantation, arsenic, Dose=4.7x10 <sup>15</sup> cm <sup>-2</sup> , Energy=70keV.                                                                             |  |  |  |

| Deposition of oxide (auto-doping prevention)                | LPCVD of oxide, thickenss=800Å                                                                                                                                    |  |  |  |

| Arsenic activation                                          | RTA: 1050°C, time=40 seconds, N2                                                                                                                                  |  |  |  |

| Oxide etching (gate, S/D)                                   | Directional RIE of oxide                                                                                                                                          |  |  |  |

| Self-aligned silicide formation                             | Titanium sputtering, thickness=500Å,<br>First RTA, 650°C, 1 min., N2,<br>Wet etching of unreacted titanium: H2O2,<br>NH4OH,<br>-Second RTA, 850°C, for 30 seconds |  |  |  |

| Deposition of oxide                                         | LPCVD of oxide, thickenss=3000Å                                                                                                                                   |  |  |  |

| Densification of oxide                                      | RTA, 800°C, 2 min.                                                                                                                                                |  |  |  |

| Formation of contact windows to gate, S/D                   | Photolithography (mask #3)                                                                                                                                        |  |  |  |

| Contact opening                                             | RIE of oxide                                                                                                                                                      |  |  |  |

| Titanium tungsten application                               | Sputtering of TiW, thickness=1000Å                                                                                                                                |  |  |  |

| Metallization                                               | Sputtering of Al layer, thickness=1µm                                                                                                                             |  |  |  |

| Metal patterning                                            | Photolithography (mask#4)<br>Aluminum and TiW wet etching(H2O2)                                                                                                   |  |  |  |

| Aluminum sintering                                          | 450°C, 25 min. forming gas                                                                                                                                        |  |  |  |

| Table 2.2: 0.8 µm [ | process summary |

|---------------------|-----------------|

|---------------------|-----------------|

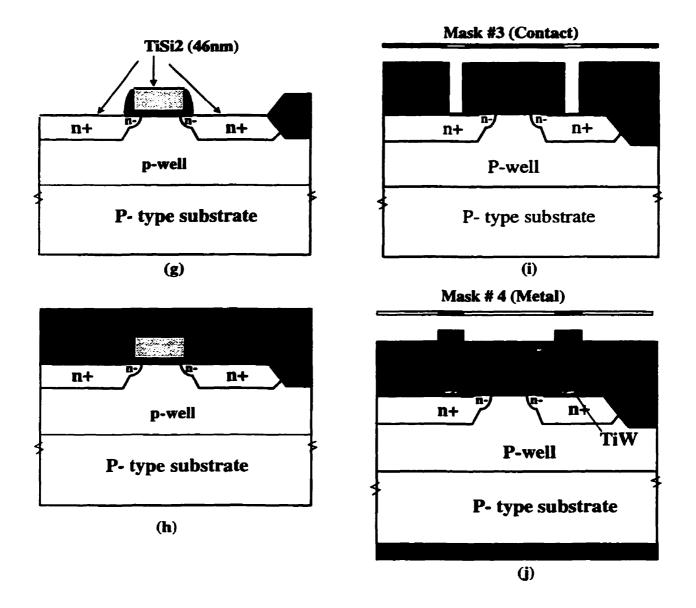

## 2.5 Layout of 1 A Power Switch

The 1-A power MOSFET switch is constructed by connecting individual unit cells in parallel using specific layout techniques. The layout pattern used here is of a checkerboard type as illustrated in Fig. 2.7, each source/drain junction is shared by four surrounding transistors, thus maximizing the effective channel width per area ratio W/A.

The 1-A power switch was realized using a pattern consisting of an array of alternating source and drain junctions, self-aligned to a mesh of polysilicon-gate structure. The width of the polysilicon line is  $0.8 \mu m$ .

Fig. 2.7: Checkerboard layout pattern using single level metallization

Alternating source/drain metal runners are composed of one level of metal (aluminum) which run diagonally over the source/drain junctions to contact the pads via wide metal buses. Both the contact and the metal runners are oriented at 45° in order to achieve minimum cell pitch. The metal runner width is kept as narrow as possible to achieve minimum cell pitch but wide enough to avoid electromigration failure due to high current densities, this is especially true in the long metal runners at the centre of the structure.

#### 2.6 Process Simulations

The process flow discussed in section 2.4 was arrived at by iterative simulations using TSUPREM-3 and TSUPREM-4[11] which were used to adjust the doping profiles of the pwell, channel, S/D junctions and LDD regions.

Since simulation of a 2-D structure defined with a fine mesh is very time consuming, 1-D simulations using TSUPREM-3 were initially used to arrive at the doping profiles, oxide layers thickness, ion-implantations doses and energies etc. Once the doping profiles and processing parameters are correctly obtained using 1-D simulations, 2-D simulations using TSUPREM-4 were carried out to account for 2-D effects such as lateral diffusion and to fine tune the final processing parameters. Further, doping profiles, device structure and mesh generated by 2-D simulations can be directly transferred to a device simulator such as MEDICI.

#### 2.6.1 2-D Process Simulations Using TSUPREM-4[11]

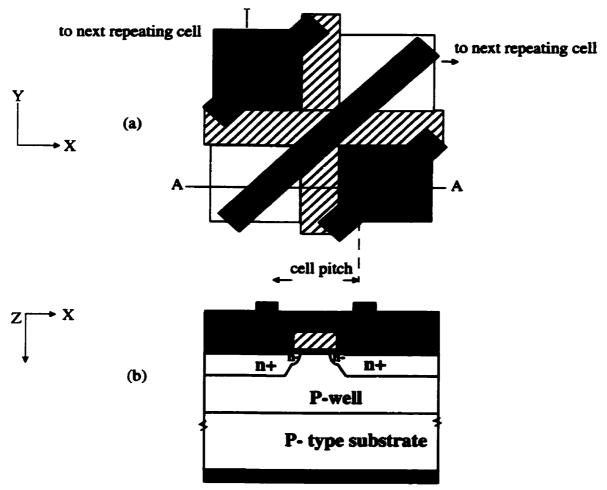

The simulated structure is essentially the unit cell of the power MOSFET switch, which is the main building block of the switch. The top view along with a cross section of the unit cell are shown in Fig. 2.8. Aggressive layout design rules were developed in order to achieve the minimum cell pitch possible. The minimum cell pitch for a given technology is determined by the minimum line width that can be resolved by this technology. In the MRL facilities this line width is 0.8  $\mu$ m, the complete design rules used in the layout is given in Appendix A.

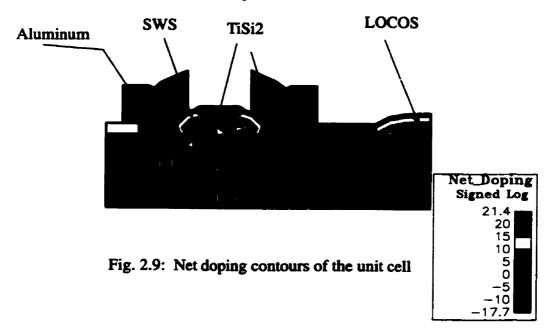

The simulated structure has a cell pitch of 4.1  $\mu$ m. The process utilizes two levels of interconnects, a polysilicon layer and a single level of metallization. The net doping contours in the different regions of the unit cell structure together with the major process components are shown in Fig. 2.9 using TMA Visual<sup>1</sup>.

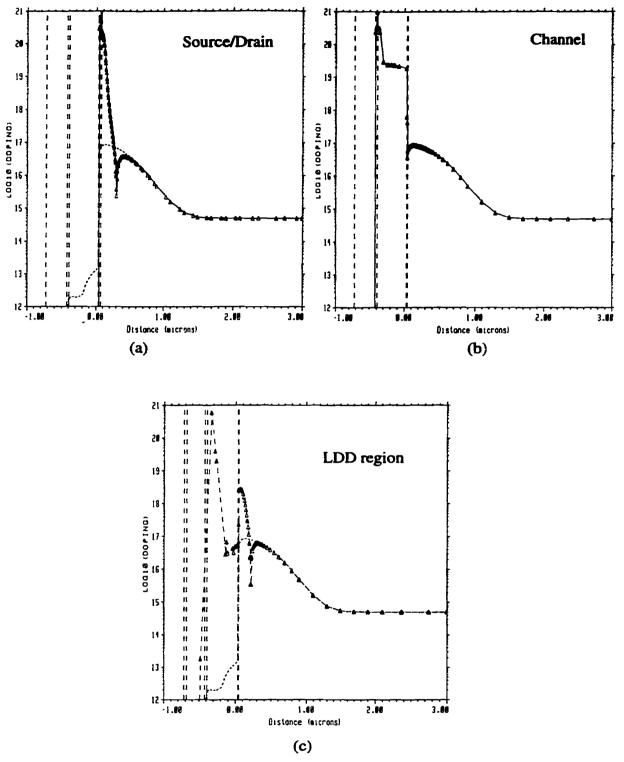

The doping profiles in the channel, source/drain regions and in the LDD are shown in Fig. 2.10. The threshold voltage adjustment using BF<sub>2</sub> results in channel surface concentration of  $8 \times 10^{16}$  cm<sup>-3</sup> corresponding to a threshold voltage of 0.322 V. The LDD regions has a junction depth of 0.18 µm and a maximum peak concentration of 2.6x10<sup>18</sup> cm<sup>-3</sup>, its width is determined by the SWS oxide lateral width which is 0.35 µm.

The S/D junction depth and doping profile are controlled by the arsenic ion-implant dose and energy and also by the thickness of the screen oxide. The surface concentration of the source/drain regions is  $2.5 \times 10^{20}$  cm<sup>-3</sup> with a junction depth of  $0.22 \mu$ m.

While all ion-implantations are performed through a screen oxide to ensure amorphous scattering of dopants, a 7° tilt angle were used in the simulations since the commercial ion-implantation facilities uses 7° tilt angle as a standard procedure. In addition, temperature ramp-up and ramp-down of all diffusion steps were included in the simulations.

<sup>1.</sup> TMA Visual is a trademark of Technology Modeling Associates, Inc. (TMA)

Fig. 2.8: Device structure: (a) top view (b) cross section of the unit cell

Fig. 2.10: Simulated doping profiles in (a) S/D region, (b) channel region and (c) LDD region

#### 2.7 Device Simulations

Device simulations were carried out using MEDICI[12]. MEDICI simulations were done iteratively in conjunction with TSUPREM-4 to adjust and/or optimize the unit cell electrical characteristics such as threshold voltage, subthreshold swing, breakdown voltage etc. The empirical formula in Equation 2-5 was used to analytically confirm the minimum device length for long channel behavior. The calculated  $L_{min}$  is 0.423 µm which suggests that a 0.8 µm device will not suffer short channel effects. The subsequent simulations results are normalized on a per channel width basis (i.e W=1 µm).

#### 2.7.1 I-V Characteristics

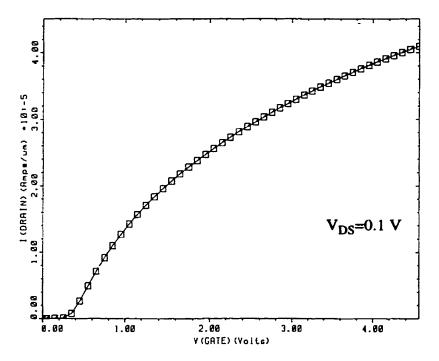

The transfer characteristic of the unit cell is obtained by sweeping the gate to source voltage from zero to 5 V in 0.1 V increments at  $V_{DS}$ = 0.1 V as shown in Fig. 2.11. The extracted threshold voltage is 0. 337 V and is defined as the intercept of the x-axis with a line extrapolated from the linear region of the I<sub>DS</sub>-V<sub>GS</sub> curve.

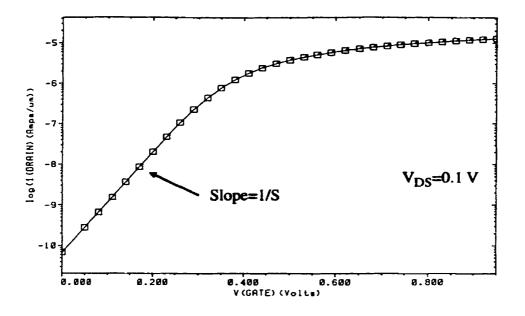

The value of the subthreshold swing S is extracted from the subthreshold transfer characteristics, as shown in Fig. 2.12, and is equal to 80.34 mV/decade at  $V_{GS}$ = 0.17 V. The device leakage current at zero gate voltage and  $V_{DS}$ = 0.1 V is 68.7 pA/µm. The unit cell effective channel length is 0.6225 µm.

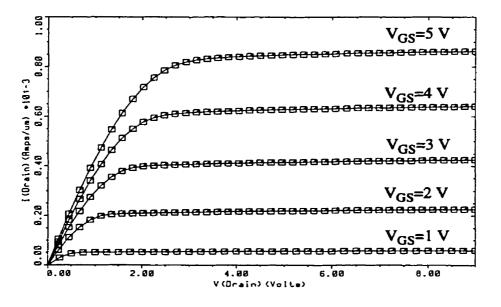

The output characteristics are simulated by sweeping  $V_{DS}$  from 0 to 9 V at different  $V_{GS}$  values from zero to 5 V in 1 V increments as shown in Fig. 2.13.

The drain saturation current  $I_{D-sat}$  is 862  $\mu$ A/ $\mu$ m at  $V_{GS}$ = 5 V which indicates high current drive of the unit cell. This result translates into the following: (1) a power MOSFET switch implemented by paralleling this unit cell would require less total width, occupy less chip area which in turn results in lower input capacitance and total gate charge and (2) faster switching speeds for digital circuits implemented on-chip. In addition, the almost flat output characteristics in the saturation region is very desirable in applications such as current mirrors.

The device specific on-resistance defined as the product of the inverse of the slope of the I<sub>D</sub>-V<sub>DS</sub> curve (normalized per channel width) in the triode region and the cell pitch is  $117.46 \,\mu\Omega.cm^2$  at V<sub>GS</sub>=3.3 V.

The 1-A power switch can be realized using a pattern consisting of a 70x70 array of alternating source and drain junctions. The total width of the power switch is 31,878  $\mu$ m corresponding to a current carrying capability of at least 1.0 A and a device on-resistance  $R_{on}$  of 90.1 m $\Omega$  at  $V_{GS}$ =3.3 V.

Fig. 2.11: Simulated transfer characteristics of the unit cell (L<sub>drawn</sub>=0.8 μm, L<sub>eff</sub>=0.6225 μm)

Fig. 2.12: Simulated subthreshold characteristics of the unit cell (L<sub>drawn</sub>=0.8 μm, L<sub>eff</sub>=0.6225 μm)

#### 2.7.2 Charge Transfer Characteristics & FOM

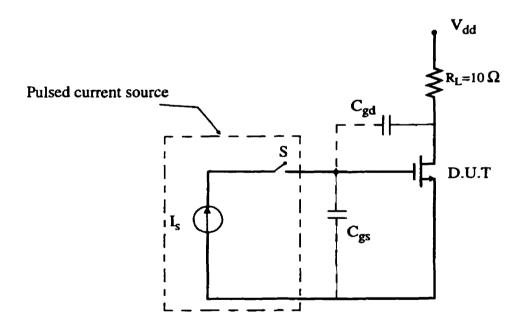

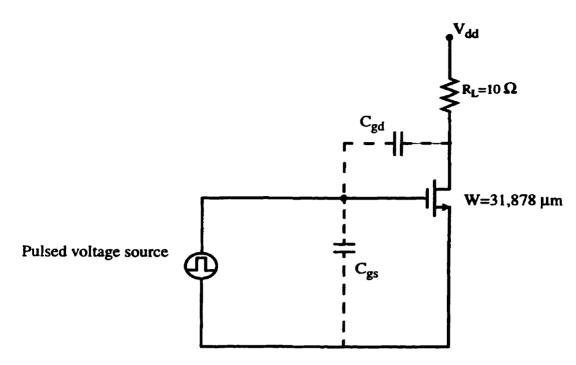

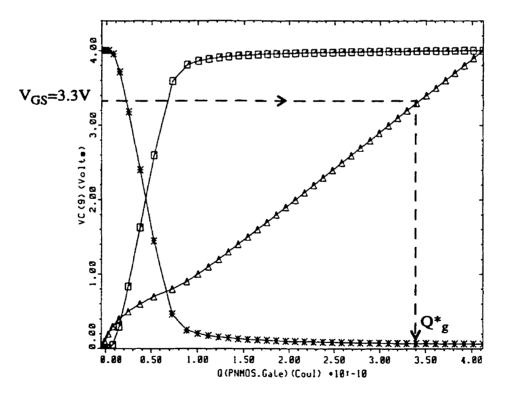

The charge transfer characteristics was obtained using MEDICI's Circuit Analysis Advanced Application Module (CA-AAM)[12]. The switch was simulated in a common source configuration as shown in Fig. 2.14 with a pulsed voltage source<sup>1</sup> applied to the gate of the switch and with the drain connected to a 10 V supply via 10  $\Omega$  load resistor. The simulated charge transfer characteristics is shown in Fig. 2.15. The total gate charge Q\*<sub>g</sub> necessary to charge the input capacitance C<sub>iss</sub> and raise its voltage to 3.3 V is 0.34 nC as illustrated in Fig. 2.15. The switch FOM defined as the product of the on-resistance and the total gate charge at V<sub>GS</sub>= 3.3 V yields a value of 30.6 m $\Omega$ nC. A summary of the key parameters of the power switch are listed in Table 2.3

| Parameter/Units                                                       | 0.8 µm/100 Å |  |

|-----------------------------------------------------------------------|--------------|--|

| Operating Voltage (V)                                                 | 3.3          |  |

| Forward blocking capability (V)                                       | 9            |  |

| Current handling capability (A)                                       | 1.0          |  |

| Active chip area (µmxµm) (excluding pads)                             | 290x290      |  |

| Total channel width (µm)                                              | 31878        |  |

| Cell pitch (µm)                                                       | 4.1          |  |

| Source/Drain junction size (µmxµm)                                    | 3.3x3.3      |  |

| Specific on-resistance ( $\mu\Omega.cm^2$ ) at V <sub>GS</sub> =3.3 V | 117.46       |  |

| On-Resistance (mΩ)                                                    | 90.1         |  |

| Total gate charge (nC) at V <sub>GS</sub> =3.3 V                      | 0.34         |  |

| $FOM=R_{on}xQ_{g}(m\Omega.nC)$                                        | 30.6         |  |

Table 2.3: 0.8 µm power switch key parameters

1. when the device is tested experimentally a pulsed current source is used to plot the gate charge versus  $V_{\rm GS}$

CMOS Compatible Power MOSFETs for On-Chip DC/DC Converters

Fig. 2.14: Schematic of test circuit used in extracting charge transfer characteristics using CA-AAM

Fig. 2.15: Simulated charge transfer characteristics of the 0.8 µm switch (W=31,878 µm)

Page 38

While the simulated FOM (30.6 m $\Omega$ .nC) for the 0.8  $\mu$ m implies significant improvement in efficiency over vertical structures, the target specification to achieve a FOM of less than 10 m $\Omega$ .nC (corresponding to 95% efficiency) cannot be achieved using such process.

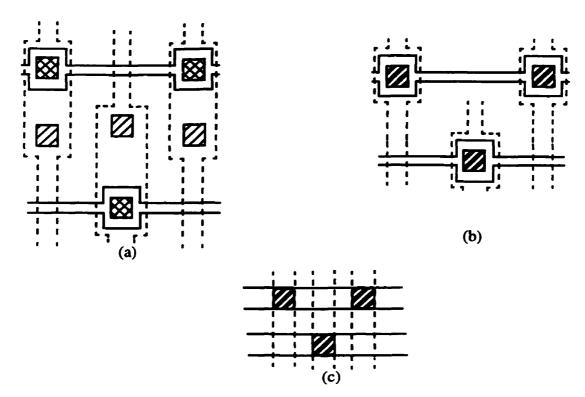

Furthermore, the simulated on-resistance does not account for the parasitic resistance of the metal runners (de-biasing effects) [13]. This resistance becomes significant in large devices. In order to reduce the resistance contribution of the metal to the on-resistance, layout patterns incorporating multilevel of metallization are necessary. Multilevel metallization also results in higher packing densities, especially, if the process features full stacking of contacts and via and/or borderless contacts are allowed [5]. Fig. 2.16 illustrates the area saving resulting from the use of stacked contacts and metal layers as well as borderless contacts.

Fig. 2.16: Stacked contacts and borderless contacts: (a) No stacking and borders, (b) stacking and borders (c) stacking and borderless

These advances enable the use of narrow-stacked metal layers as metal runners, as a result they can accommodate high current densities without the need for wide metal runners.

Deep submicron processes available today offer multilevel metallization and features such as full stacking of metal layers, contact and via are becoming standard due to advances in contact fabrication processes. In addition, and most importantly they offer high current drive and high packing density. The 1-A power switch specifications can therefore be greatly improved by using deep-submicron CMOS process technology. In Chapter 3, a 1-A power MOSFET switch implemented in 0.25  $\mu$ m-5 level metallization process is investigated in an effort to further improve the performance of the switch and to achieve a FOM less than 10 m $\Omega$ .nC.

#### 2.8 Summary

This chapter presented the design of 1-A power MOSFET switch in low voltage CMOS technology. The design uses a 0.8  $\mu$ m - single level metal process. Fabrication steps, design issues, layout techniques and simulation results were discussed. The switch was constructed using a checkerboard layout pattern to maximize the W/A ratio resulting in an active chip area of 290×290  $\mu$ m<sup>2</sup> corresponding to a total width of 31,878  $\mu$ m. Simulation results show a specific on-resistance of 117.46  $\mu$ Ω.cm<sup>2</sup>. The switch FOM is 30.6 mΩ.nC which compares favorably with commercial devices based on vertical structures rated at 20-30 V, however, it fell short of achieving the targeted 10 mΩ.nC.

## References

- [1] D. A. Johns, K. W. Martin, "Analog Integrated Circuit Design", John Wiley & Sons, New York, 1997.

- [2] Bin Yu, "MOSFET Technology for Ultra-Large-Scale Integration", Ph.D. Dissertation, University of California at Berkeley, 1997.

- [3] S. M. Sze, "Physics of Semiconductor Devices", Wiley, New York, 1981.

- [4] L. D. Pede, "A 1 V Low Power CMOS Process", M. A. Sc. Thesis, University of Toronto, 1998

- [5] C. Y. Chang, S. M. Sze, "ULSI Technology", McGraw-Hill, Inc., New York, 1996.

- [6] P. J. Tsang, S. Ogura, W. W. Walker, J. F. Shpard and D. L. Critchlow, "Fabrication of High-Performance LDDFET's with Oxide Sidewall-Spacer Technology", IEEE Transactions on Electron Devices, vol. ED-29, pp. 590-596, 1982.

- [7] S. Ogura, P. J. Tsang, W. W. Walker, D. L. Critchlow, J. F. Shepard, "Design and Characteristics of the Lightly Doped Drain-Source (LDD) Insulated Gate Field-Effect Transistor", IEEE Transactions on Electron Devices, vol. ED-27, pp. 1359-1367, 1980.

- [8] C. A. T. Salama, "Introduction to Integrated Circuit Engineering", Course Notes, 1996.

- [9] C. K. Lau, Y. C. See, D.B. Scot, J. M. Bridges, S. M. Perna, R. D. Davies, "Titanium Disilicide Self-Aligned Source/Drain + G Technology", IEEE International Electron Device Meeting (IEDM), Proceedings, pp. 714-717, 1982.

- [10] M. E. Alperin, T. C. Hollaway, R. A. Haken, C. D. Gosmeyer, R. V. Karnaugh, W. D. Parmantie, "Development of the Self-Aligned Titanium Silicide Process for VLSI Applications" IEEE Journal of Solid-State Circuits, Vol. sc-20, pp. 61-69, 1985.

- [11] TSUPREM4<sup>TM</sup>, Two-Dimensional Process Simulation Program, User's Manual, Version 6.5, Technology Modeling Associates, Inc., 1997.

- [12] Medici<sup>TM</sup>, Two-Dimensional Device Simulation Program, User's Manual, Version 4.0, Technology Modeling Associates, Inc., 1997.

- [13] M. Darwish, J. Huang, M. Liu, M. Shekar, R. Williams, M. Cornel, "Scaling Issues in Lateral Power MOSFETs" International Symposium on Power Semiconductor Devices & ICs (ISPSD), Proceedings, pp. 329-332, 1998.

# **CHAPTER 3**

## 1-A Power MOSFET in 0.25 µm CMOS Technology

#### 3.1 Introduction

The performance of the power switch presented in Chapter 2 and implemented in 0.8  $\mu$ m base line and single level metallization can be significantly improved through device scaling and the use of multiple level metallization. Using an advanced deep-submicron technology can result in a substantial increase in the packing density due to the shorter channel length, the smaller contact areas and spacing as well as the use of contacts stacking and multi level metallization.

Associated with the increase in packing density is a smaller specific on-resistance and higher current drive. The higher the current drive the smaller the required total width of the power switch, resulting in reduced input capacitance and gate charge.

In this Chapter, the design and implementation of a 1 A N-channel power switch implemented in a 0.25  $\mu$ m, 5 level metallization CMOS process is presented. Simulation of the 0.25  $\mu$ m unit cell was carried out in order to predict the performance of a device fabricated in such technology. Experimental results are presented and the measured parameters are compared with simulation results.

## **3.2 The 0.25 μm MOSFET Unit Cell**

To predict the performance of the 0.25  $\mu$ m power MOSFET switch, process and device simulations were performed for the unit cell<sup>\*</sup>. Simulations can provide a reasonable insight on the extent of performance improvements one might obtain by the scaled-down process.

Suppression of short channel effects (SCE) constitute the main design challenge in a scaled-down process. A solution to alleviate short channel effects is the use of lateral channel doping engineering such as pocket and halo implant which provide the possibility to effectively tailor the short-channel performance[1].

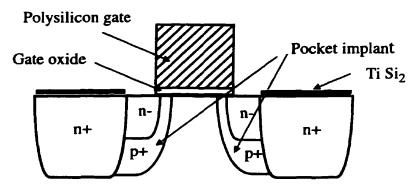

The pocket implant, illustrated in Fig. 3.1, raises the concentration of the p-well around the source and drain junctions without increasing the concentration in most of the channel region, hence, the depletion region widths, responsible for SCE, are reduced and the channel carrier mobility is not significantly degraded.

Fig. 3.1: Cross section of an LDD MOSFET including pocket implant

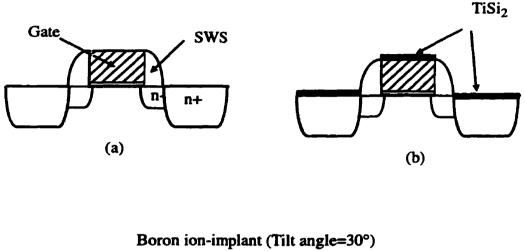

A technique used to implement the pocket implant involves the use of large-angle-tilt (LAT) implantation[2-3] in which the ion beam is oriented by a large angle, typically, 30° to 40° and the implantation is masked by the gate electrode and a  $TiSi_2$  film. The stopping power of  $TiSi_2$  is 1.5 times that of silicon, therefore, by adjusting the dose, energy and the

University of Toronto

<sup>\*.</sup> The manufacturer's documentation provided most of the information on the structure and the process used in this fabrication. This information is proprietary.

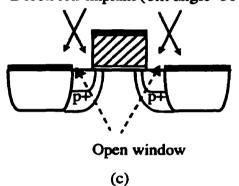

tilt angle of the ion-implant, very localized pocket profiles can be fabricated using this method. Process sequence of the pocket fabrication are illustrated in Fig. 3.2.

Fig. 3.2: Steps for pocket implant fabrication (a) LDD and S/D implantation (b) salicide formation (c) SWS removal and LAT ion-implantation

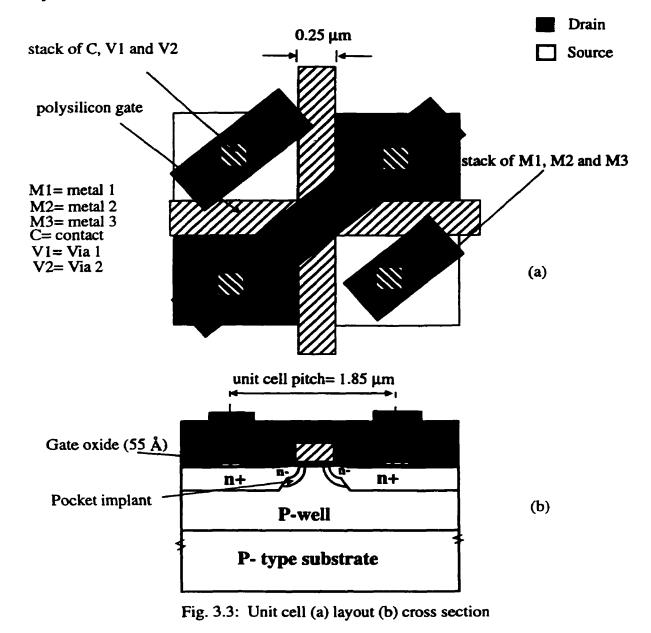

Process simulations were carried out for a unit cell of 1.85  $\mu$ m cell pitch which was used in the layout of the power switch. The structure is the same as the one used for the 0.8  $\mu$ m with the proper scaling of the gate length, source/drain junction depths, oxide thickness and p-well doping profile with the only major difference being the incorporation of the pocket implant.

#### Page 44

#### 3.2.1 Layout of the 0.25 µm Unit Cell

The layout of the unit cell is illustrated in Fig. 3.3a which is the main building block of the power switch. The channel length used in the layout of the unit cell is 0.25  $\mu$ m. The ability to stack multiple contact and vias as well as metal layers resulted in a cell pitch of 1.85  $\mu$ m. The minimum widths of the metal layers used in the layout are dictated by electromigration guidelines as suggested by the manufacturer. Using too thin metal runners may result in switch faliure.

CMOS Compatible Power MOSFETs for On-Chip DC/DC Converters Universit

# **NOTE TO USERS**

Page(s) not included in the original manuscript are unavailable from the author or university. The manuscript was microfilmed as received.

> 45 and 46 (Section 3.2.2)

This reproduction is the best copy available.

# UMI

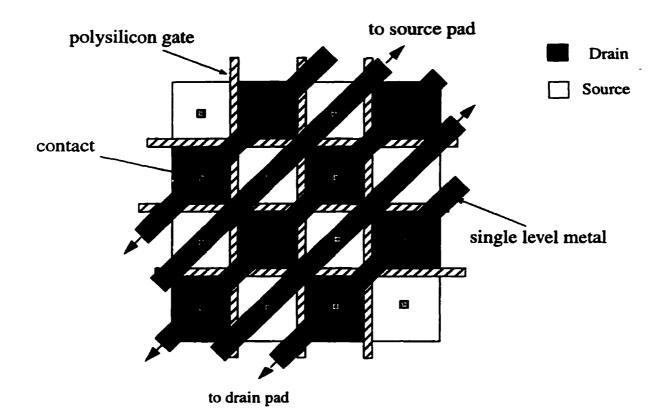

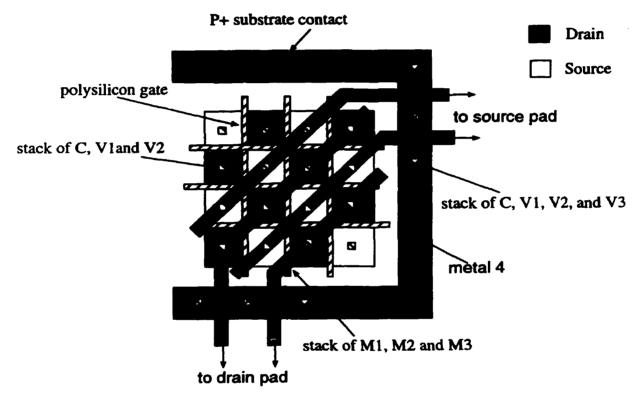

## 3.3 0.25 µm Power MOSFET Switch Layout

A checkerboard layout pattern was used in the layout of the 1 A - 0.25  $\mu$ m power MOSFET switch. The layout shown in Fig. 3.7, uses: (1) a stack of 3 metal layers to reduce the cell pitch and minimize the de-biasing effects and (2) a p+ substrate contact on the surface.

A power switch with a 1 A current carrying capability can be constructed using a  $63 \times 63$  array of alternating source and drain junctions equivalent to a total channel width of 12,499 µm and exhibiting an on-resistance  $R_{on}$  of 61 m $\Omega$ .

Fig. 3.7: Checkerboard layout pattern for the 0.25 µm switch

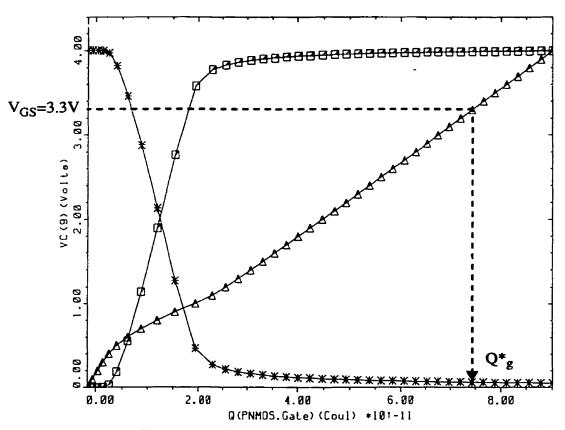

## 3.3.1 Charge Transfer Characteristics and Figure Of Merit (FOM)

The charge transfer characteristics of the device were obtained using the MEDICI CA-AAM software package and the circuit configurations is shown in Figure 2.14 and discussed in Section 2.7.

CMOS Compatible Power MOSFETs for On-Chip DC/DC Converters University of Toronto